Esta breve serie de lecciones semi cortos en Verilog se significa como una introducción a la lengua y a que los lectores para profundizar en el diseño FPGA.

Estos tutoriales asumen que está familiarizado con los circuitos de lógica básicos y ecuaciones de lógica, así como asociados comportamientos.

Plantean esta pregunta a usted: Si F = (A • B) y A es lógica alta y B es de lógica baja, ¿qué es F? Si usted no puede responder a esta pregunta, te recomiendo que visites a tus estudios de circuito lógico. Circuito lógico tutoriales son una posibilidad si se realizan suficientes solicitudes.

Lista de cosas básicas a saber antes de comenzar:

-Las funciones de las puertas lógicas básicas (AND, OR, NAND, XOR...)

-La diferencia entre la "lógica del alta" y "poco lógica" y que está representada por un "1" y que por un "0"

Familiaridad con C y C++ es útil (a veces) pero no es necesario en absoluto.

Si estás preparado para seguir este tutorial, necesita dos cosas:

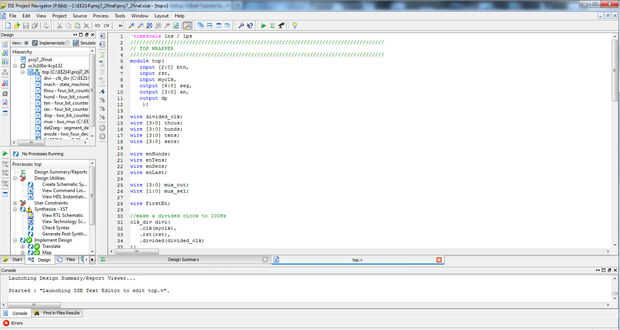

-Un IDE para el Verilog (recomiendo Xilinx ISE Design Suite; después de registrarte gratis te puede descargar este IDE muy robusto)

-Un tablero de diseño digital de FPGA (yo prefiero las placas Digilent Inc. por su facilidad de uso y diseño "duro a la ruina")

Hay amplia documentación sobre el ISE ahi por lo que no se va sobre cómo utilizar el software.

La imagen de esta introducción es de una típica ventana ISE con editor de texto, directorio del módulo y panel de proceso abierto.

Ah y en alguna diapositiva verás títulos que comienzan con VM x.x; Esto está parado para el módulo de Verilog y hace un poco más fácil el seguimiento de.

En Verilog.