Paso 9: Preparación para programar la FPGA Junta

Así es, la UCF.

Mientras que, como mencionamos antes, cada fabricante de tablero de diseño digital tiene limitaciones diferentes para las distintas placas. Una restricción de la muestra es la siguiente:

RED "conducido" LOC = "M5";

NET precede a cada declaración, seguido por el nombre de la red (entre comillas) y, a continuación, la restricción de ubicación real (también entre comillas). El nombre puede ajustarse a lo que el ingeniero desea (aunque los mejores nombres son aquellos que transmiten más significado en la menor cantidad de espacio) y la restricción de ubicación indica que la «red» está conectada físicamente el FPGA. Un Comentario en un UCF está indicado diferentemente que en el módulo de Verilog; en UCF, use un '#' para denotar un comentario. Algunos IDEs han construido en características que le permiten al código de lote comentario fuera resaltando el código deseado y presionar un botón o combinación de teclas de acceso rápido en el IDE.

Así que si tuviera que ir a través y crear un archivo UCF para su placa, que contiene una restricción para cada entrada y salida, el IDE sería capaz de crear un flujo de bits para su placa FPGA, en conjunto con el módulo de Verilog que creó anteriormente.

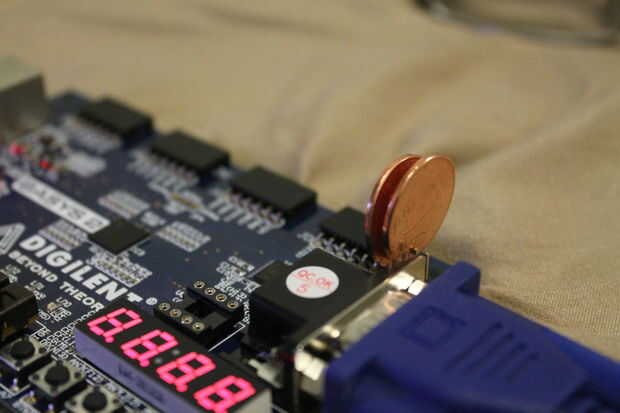

El proceso para programar diferentes tableros FPGA varía, así que consulte a su fabricante para obtener instrucciones específicas. La foto incluida es de mi tabla FPGA más mi reemplazo de puente del pin de ciento dos (temporal y no se recomienda hacerlo a menos que absolutamente debe continuar depuración como debía).

Nota: módulos de Verilog se almacenan en archivos con la extensión .v y UCF archivos en un formato .ucf. Ambos archivos son editables con bloc de notas o cualquier editor de texto (Wordpad tiende a respetar reglas de sangría mejores que el Bloc de notas).