Paso 12: VM 3.0: diseño Modular

Por ahora debería ser capaz de implementar funciones de simple lógica usando los operadores básicos de Verilog (| &,...) y a ejecutar correctamente en la placa de la FPGA. Si no estás absolutamente a esa etapa, por favor comience con VM 2.0.

En "VM: mi primer Verilog proyecto 2.0", introduje el concepto de "módulos" y "modular" código; Ahora hay unos cuantos matices de módulos que necesita saber para ser un dominio "diseño modular". Pero primero tenemos que hablar "¿Qué es el diseño Modular?

Si finalizado el ejercicio "hello_world", fueron introducidos a la palabra "módulo" del Verilog. Cada archivo Verilog de la fuente contiene una y sólo una definición de módulo. Entonces, ¿cómo podemos crear proyectos complejos que implican muchos módulos más pequeños? Vamos a tomar el ejemplo de la construcción de un contador de tiempo controlados circuito del LED. ¿Necesitamos en nuestro circuito para que un LED parpadee cada segundo si algún interruptor estaba una lógica uno y sólo un reloj de 50MHz?

Romper lo que tenemos en tres tipos: entradas, salidas y los componentes internos.

Entradas: fuentes de señal física como un oscilador ("reloj"), interruptores, botones, puertos de datos, etc....

Salidas: salidas de físicas que serán conducidos por el circuito como LEDs, puertos de datos, pantallas, etc....

Componentes internos: componentes que toman el estado de las entradas para generar una salida deseada; no todos estos tienen que ser conectados a los puertos de "nivel superior", pero finalmente todo debe "ruta".

Leer estas clasificaciones es de vital importancia que sabes las diferencias! Tenga en cuenta también, las palabras nuevas de vocabulario: "nivel superior" y "ruta".

Pensar en lo que podría significar estos términos... Formalmente, a definirlos en un minuto.

Comparan estos tres tipos de componentes de una ecuación algebraica, las entradas son las variables independientes, las salidas son las variables dependientes y los componentes internos representan la ecuación real. Recordando esta analogía le ayudará a decidir cuando se trabaja en proyectos de si un componente es un componente interno, entrada y salida.

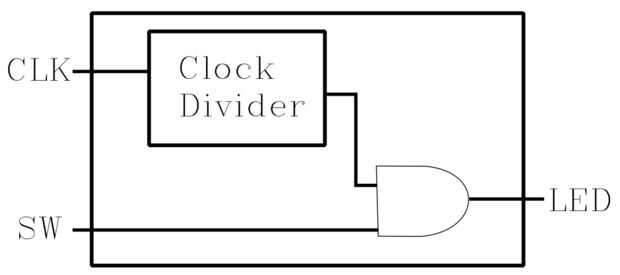

En el caso del circuito de parpadeo de LED, aquí es lo que tenemos en un nivel muy alto:

Entradas: 50 MHz reloj, interruptor

Salidas: LED

Elementos internos: A 50 MHz a 1 Hz reloj divisor, una puerta y (porque el LED debe solamente encendido si tanto el reloj dividido y el interruptor de lógica uno)

¿Cómo, en un nivel muy alto (es decir, en su mayoría "cajas negras" para representar componentes en lugar de patrones de la puerta), bloque diagrama de este circuito? Recuerde que usted puede hacer un divisor de reloj por conectar una cantidad de D-Flip Flops (DFFs) juntos junto a algunos inversores.

Ver el esquema adjunto de la respuesta.

Reto: En realidad, tendríamos un botón físico que reiniciará todos los DFFs en el divisor del reloj. ¿Puede dibujar el origen y destino de un botón llamado "RST" en este diagrama de bloques?

Diagramas de bloques como este son el primer paso para ayudarle a que averiguar cómo escribir un programa de Verilog, como cada caja en el diagrama terminará como una instancia de un módulo de código. Aviso de que tenemos un gran bloque que contiene un número de bloques más pequeños; llamamos a esto el módulo de "top". El módulo de "top" es lo que se encarga de conectar todos los componentes internos del circuito para salidas y entradas físicas.

Dentro de este módulo superior particular son dos cosas: un divisor de reloj y una puerta y. Pero observe que el bloque divisor de reloj también contiene un número de bloques más pequeños (DFFs). NO tenemos que crear estos DFFs en nuestro módulo superior; podemos crear un módulo de divisor de reloj separada que contiene todos los DFFs y crear una instancia de ese divisor de reloj en nuestro módulo superior.

Como puede haber adivinado, también tenemos que hacer un módulo de facto que nos podemos crear una instancia de un número de veces en el divisor del reloj. Esto nos permite sólo definen el comportamiento de un D-Flip Flop una vez, luego crear una instancia de varias instancias de de facto. Todo lo que tenemos que hacer en nuestro Verilog código es conectarse cada instancia de la DFF los puertos apropiados (es decir, conectar sus entradas y salidas), pero más en la creación de instancias de módulo más adelante.

Nota: No intentar este proyecto LED parpadea el código todavía; hay unas cuantas cosas más que tenemos que cubrir.

El punto de este módulo es para exponerle a diseño modular; ¿ves por qué llamar estos tutoriales "módulos"? Esta idea debe arraigada en tu mente mientras continúas aprendiendo y utilizando Verilog.