Paso 16: VM 3.3: creación de instancias temas avanzados

(Imagen originalmente creado por Digilent Inc.; modificado por mi para que esto este tutorial)

El módulo anterior había introducido y que condujo el país, el concepto de creación de instancias en Verilog. Ahora tomaremos un vistazo a un par temas avanzados (segundo tema a agregar pronto) sobre creación de instancias de módulo.

Contrarrestar la creación de instancias de control:

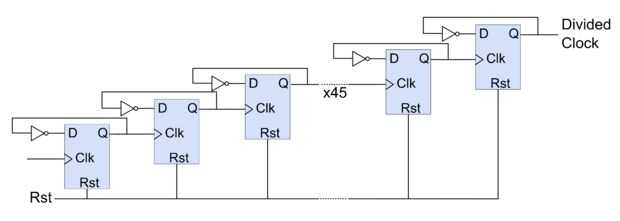

Qué pasa si necesitamos generar un montón (tomar 50 como ejemplo) de DFFs que estaban todos conectados entre sí en un circuito divisor de reloj... Ya sabemos cómo hacer un módulo general de facto, así que ahora que tenemos que crear instancias 50 veces y conectar el pin de reloj de cada uno a la salida de las FDF que es secuencialmente antes de él, conectar reset para un reinicio global y el D en pin al inverso de la salida de la DFF (Q). Utilice el esquema adjunto para referencia.

Esto sería un montón de instancias para escribir (50 instancias veces 6 líneas por instanciación es 300 líneas!) a mano. Pero en Verilog podemos utilizar un controlador de contador de bucle, en concreto, un bucle "for" para crear una instancia (generar) todos estos módulos (excepto la primera) para nosotros en muy pocas líneas de código. Pero hay una salvedad; tenemos que planificar cuidadosamente nuestro diseño para que podemos usar un "loop genera" correctamente.

Observe que la forma nos conectamos cada de facto a la siguiente es uniforme y predecible. Por supuesto, reloj de facto la primera será el reloj de la entrada de nuestro módulo de nivel superior y la salida del último de facto irá en alguna parte en el módulo de nivel superior, pero podemos abordar aquellos individualmente; durante la generación, cada interno en el diseño salvo el primer reloj que designaremos manualmente y el hilo de salida último explícitamente darán una fuente y un drenaje. El software sabe que los dos cables restantes necesitan ya sea una fuente (primer reloj) o drenaje (últimos datos) y es responsabilidad del ingeniero proporcionar uno.

Como se mencionó anteriormente, usted tiene que configurar el diseño correctamente con el fin de utilizar un bucle de generar. ¿En qué consiste esto? Bueno, es lógico desde cada DFF va a tener un reloj en dependiente sobre el anterior (no incluyendo el primero de ellos!) que podemos agrupar estas señales similares en un autobús! Esto nos permite hacer referencia a grupos de señal como una matriz en C/C++ y llamada los conductores índice utilizando el operador [].

El pin de reset de cada DFF vendrá de un reset común, ya que cada DFF necesita poder restablecer al mismo tiempo.

Sin saber los detalles de un bucle de generar sin embargo, todavía podemos hacer nuestros autobuses que se utilizarán en el diseño. ¿Qué tipo de autobús hará? Ya que estos llevan sólo una señal de una fuente a un desagüe, hacemos los cables.

alambre hacia fuera [49:0] //50 bit bus amplia para entrada y salida de facto

También podemos crear nuestro primer DFF. Utiliza el módulo de facto de Tutorial módulo 3.2 y suponiendo que nuestro divisor del reloj tiene una entrada clk (un pin de reloj), una primera entrada (un pin de reset) y una salida hacia fuera (digamos que impulsará un LED, creando un efecto de parpadeo).

(de facto) dff0

.CLK(CLK),

.RST(RST),

. D(~OUT[0]),

. Q(OUT[0])

);

Ahora, el bucle de generar. Es similar a un bucle en C y C++ pero tiene sus propios matices. Primero necesitamos crear una variable contador. En Verilog el tipo variable se llama "genvar" y se utiliza para declarar una variable, lo llaman "y", así:

genvar y;

El bucle de generar comienza con la palabra clave "generar" y termina con "endgenerate".

Nota: Se debe declarar cualquier variable genvar fuera del ámbito del bucle generar.

Ahora tenemos:

genvar y; endgenerate

generar

Inmediatamente después de la palabra "generar" es el lazo real. Su declaración es como un bucle en C y C++, pero en Verilog, tenemos el lujo de izquierda y derecha rizados llaves ({y}) pero tenemos el equivalente de Verilog: comienzan y terminan. Además, Verilog no admite operaciones de postfix, por lo que no puede indicar "y ++" y deberá indicar en su lugar "y = y + 1". Al construir el bucle, tenga en cuenta que ya creamos la primera DFF (DFF0) por lo que nos va a generar de 1 a 49 (menores de 50).

genvar y; final

generar

para (y = 1; y < 50; y = y + 1) //spaces puede omitirse

comenzar

endgenerate

Con un lazo de generar, va a "empezar" un bucle de creación de instancias y debe darle un nombre a este proceso. No utiliza este nombre para cualquier otro propósito y no se referirá a él más adelante en nuestro diseño (se utiliza internamente en el sintetizador). Hacemos esto mediante la adición de una declaración siguiendo el formato ":" y colocar en la misma línea que el "empezar" de buen estilo. Llamemos a esta "dff_generation":

genvar y; final

generar

para (y = 1; y < 50; y = y + 1) //spaces puede omitirse

comenzar: dff_generation

endgenerate

Ahora es la parte más difícil y crucial: creando el modelo de creación de instancias. Esto se verá como cualquier otra creación de instancias salvo que los cables se pasa el módulo se pueden utilizar el genvar como modificador del valor o valor. Hay que recordar que valor de genvar va a cambiar por uno en este caso después de cada ejecución.

En lugar de caminar a través de cada línea de la creación de instancias le daremos todo el bloque de código y señalar cosas que no puede reconocer. Asegúrese de ver la imagen proporcionada para ver cómo se implementa este circuito.

genvar y;

generar

para (y = 1; y < 50; y = y + 1) //spaces puede omitirse

comenzar: dff_generation

la siguiente instancia nombre no importa

(de facto) dff_insts

.CLK(OUT[y-1]), //clk en de facto "y" está fuera de "y-1"

.RST(RST), //each DFF obtiene el mismo reset

. D(~OUT[y]), //input se alimenta la salida invertida

. Q(OUT[y]) //output

);

final

endgenerate

Le animo a mano traza unas cuantas iteraciones del bucle para ver cómo la generación proceso de obras. El sintetizador dará cada instancia crea un único nombre indexado como "dff_insts1" y "dff_insts2".