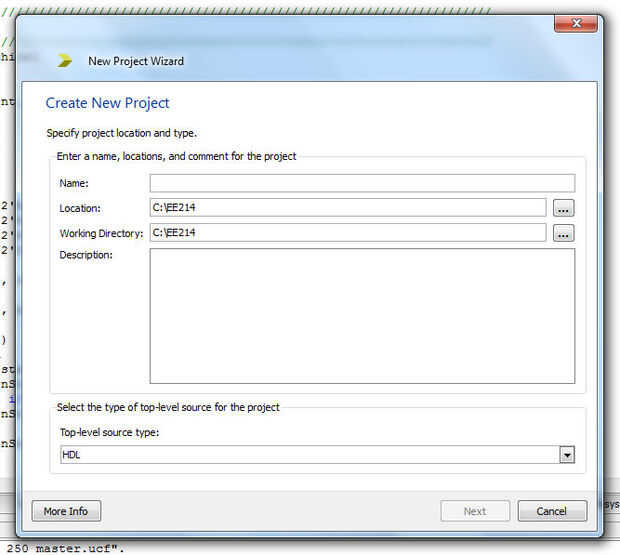

Paso 3: VM 2.0: su primer proyecto de Verilog

A pesar de que apenas se exponen a Verilog, creo que usted aprenderá mejor al saltar derecho a la piscina de HDL. No te preocupes aunque, caminaremos a través de todo el código junto, y estaré seguro de explicar por qué y cómo funcionan las cosas. Aprendí la manera dura que Verilog se basa en sí mismo muy rápidamente, por lo que corresponde a obtener una base sólida de comprensión.

Nota: A pesar de lo conveniente es copiar y pegar el código, le recomiendo que escriba de nuevo todo para que lo entiendas mejor. Pruébalo; trabaja.

Antes de comenzar, quiero que usted preste especial atención a los siguientes rasgos de mi código:

• Minúsculas: Verilog es sensible a mayúsculas. Palabras clave se debe escribir con la cubierta apropiada (minuscula) y cualquier usuario nombrada de entradas, salidas y otras piezas de código siempre debe ser referida a como ellos fueron primero declarados.

• Sangría: aunque no tan evidente en este ejemplo, indentación es un gran problema en Verilog (como con muchos otros lenguajes de programación). Mientras que el compilador y el software suite funciona con código mal formateado, es estilo pobre a no observar las reglas de sangría (que se explicará más adelante).

Así que sin más preámbulos, aquí está, en mi opinión, el equivalente a "Hola, mundo" en Verilog:

----------------------------------------------------

' calendario 1ns / ps

Este es un Comentario en Verilog

hola_mundo () módulo

interruptor de entrada [0]

interruptor de entrada [1],

salida de led

);

asignar led = interruptor [0] & ~ interruptor [1];

endmodule

------------------------------------------------------

Ahora, esto no es la implementación más eficiente del módulo. Vamos a empezar a buscar en el código de pieza por pieza y ver si puede averiguar cómo podrían mejorarlo.