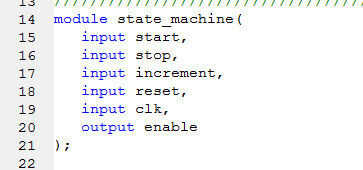

Paso 6: El módulo de declaración

interruptor de entrada [0]

interruptor de entrada [1],

salida de led

);

módulo es una palabra clave de Verilog. Piense en ello como una declaración de tipo; en C++ podemos tener una declaración de la función de "vacío hello_world (< parámetros aquí >)". ¿Notar las similitudes?

Mientras que Verilog no devuelve ningún valor (como una función de C++ "vacía") y realmente no es una función, su sintaxis es similar y todavía podemos pensar el módulo como una declaración de tipo y "hello_world" como el nombre (nombres en Verilog no pueden contener espacios). Código de Verilog buena es "modular", y analizaremos lo que significa (más tutoriales pronto estará disponibles en mi sitio web personal y posiblemente Instructables).

Dentro de los paréntesis de la declaración son lo que nos podemos comparar como nuestra lista de parámetros. Es decir, el módulo tiene una entrada llamada interruptor [0], otra entrada llamado interruptor [1] y una salida llamada led. entrada y salida son esencialmente tipos de variables. Hay algunas peculiaridades a las declaraciones de módulo que veremos en el siguiente módulo.

¿Ves cómo podríamos reducir nuestra entrada y salida de las declaraciones de tres declaraciones a dos?

Sugerencia: Puede crear matrices (llamados autobuses) en Verilog.

Después se declaran todas las entradas y salidas, se cierra la lista de parámetros con un correspondiente paréntesis y un punto y coma. El punto y coma, igual que en C++, marca el "fin" de una declaración. Una conveniencia de Verilog es poder dividir grandes declaraciones como lógica largas en varias líneas para facilitar la lectura, como no olvidar el punto y coma.

La imagen muestra la codificación de color típico de la declaración de un módulo.