Paso 7: Lógica en Verilog

Esta línea es donde sucede la "magia". Hasta este punto, el código ha descrito todas las entradas y salidas, y ahora será manipular salidas partiendo de los insumos. asignar es otra palabra clave de Verilog; Usted usará una y otra vez. Asignar las declaraciones son descripciones permanentes de una salida basada en una o más entradas. No puede tener más de una declaración de asignar por salida, pero usted puede tener más de una expresión lógica simple por asignación. El más cercano equivalente a una asignación de C++ es establecer a una variable igual a un valor, sólo en Verilog se puede cambiar el "valor" después de que se encuentra ya tras su configuración, el valor depende de los Estados físicos de entradas.

Recuerde, Verilog es un lenguaje de descripción de hardware, es decir usted solo está describiendo cómo se comporta un circuito. Los Estados de [0] y el interruptor [1] pueden cambiar mientras el circuito esté activado (por ejemplo, le da la vuelta interruptor [0] para baja tensión lógica) pero la instrucción de asignación es firme; llevó la voluntad sólo ser conducido a alta tensión lógica en "cambiar [0] & ~ interruptor [1]".

¿Qué pasa con "interruptor [0] & ~ interruptor [1]"? ¿Entradas, pero lo que no sabemos tanto el '&' y ' ~ ' significa?

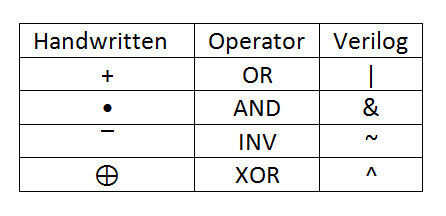

Cuando nosotros escribir ecuaciones de lógica de circuitos digitales, utilizamos un '•' de y, '+' para OR, ⊕ para XOR y si queremos indicar el inverso, o "no" de un término, dibujamos una barra sobre él. Hay equivalentes para todos estos y más en Verilog, como se ve en la tabla adjunta.

Podemos agrupar declaraciones de uso de paréntesis; Esto es especialmente útil para la creación de la NAND, NOR, y puertas XNOR, aplicamos la ecuación como haríamos para la versión no-invertida de la puerta, agregar paréntesis alrededor de la ecuación como añadirán un ' ~ ' a su frente. Por ejemplo, para hacer la declaración de Verilog de "F es igual a una xnor B", en ¿empezamos? Seguramente tenemos que "asigna" F un valor de codificación tan "asignar F =" sería un buen comienzo... OK, así que una xnor B.... No tenemos un símbolo de xnor. No te preocupes, podemos hacer A XOR B entonces invertir el término completo! Esto conduce a una solución final de "asignar F = ~(A ^ B);"

Tenga en cuenta la precedencia de operador; el operador "INV" se asocia el término a su izquierda y el y, o, XOR, etc. Siga las reglas de precedencia de ecuación lógica estándar.

No olviden el punto y coma después de la instrucción de asignación.

Para volver a nuestro ejemplo, asignar led = interruptor [0] & ~ interruptor [1]; medios que impulsará a alta tensión lógica si y sólo si interruptor [0] es una lógica «uno» y switch [1] es una lógica «cero».