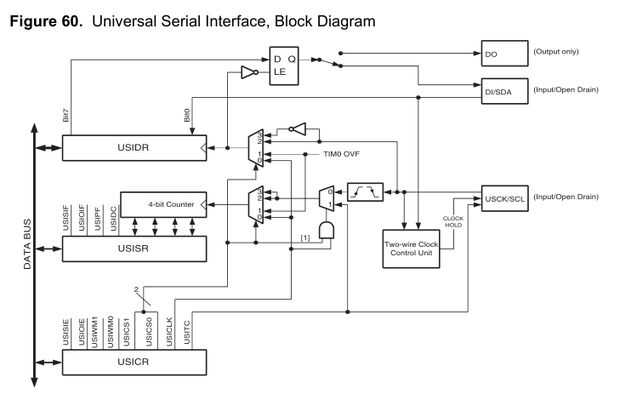

Paso 5: Implementación de código abierto I2C ATTiny USI - USI Hardware

El hardware USI tiene tres pines:

HACER - salida de datos, utilizada para tres hilos (SPI) modo de comunicación sólo

DI/SDA - datos de entrada serie, utilizada como SDA en configuración I2C

USCK/SCL - reloj, utilizado como SCK en configuración I2C

Además, el hardware USI tiene tres registros:

Datos de cambios USIDR - USI cambio de registro de datos - dentro y fuera del hardware USI

USISR - USI Status Register - tiene indicadores de estado y contador de 4 bits (más sobre esto abajo)

USICR - registro de Control de USI - se permite interrupción, modos de reloj y las funciones del software reloj Flash

Contador de 4 bits

El contador de 4 bits ocupa los 4 bits más bajos de USISR y se utiliza el tiempo de las interrupciones de desbordamiento cuando funciona en modo esclavo así como para generar pulsos de reloj SCK en modo maestro. Ser un contador de 4 bits, cuenta hacia arriba de 0 a 15 antes de desbordamiento. A rebosar, que puede desencadenar una interrupción (USI_OVERFLOW_vect, habilitado por un poco de USICR). Esto se utiliza para la tabla de estado esclavista USI de transmisión como alterna entre Estados de transmisión (más sobre esto en la sección de código auxiliar).

Cuando actúa como un maestro, el contador de 4 bits se utiliza junto con el pedacito de luz estroboscópica de reloj en USICR para generar el reloj SCK. Se establece el contador de desbordamiento en el número de impulsos de reloj que desee generar (generalmente 8 o 1, con 8 ser una transmisión de datos y 1 siendo una transmisión ACK/NACK). Entonces, usted lazo hasta el desbordamiento del contador, ajuste continuamente el bit de reloj Flash y realizar una espera de retraso. Más sobre esto pueden verse en la sección de código.

Unidad de Control de reloj de dos hilos (Detector de condición de inicio)

La unidad de Control del reloj de TWI es un módulo en la USI que monitorea la línea SCK para iniciar y detener las condiciones. Su propósito primario es el detector de condición de inicio, que, cuando está activado, genera una interrupción de USI_START_vect cuando detecta una condición de inicio válido. Este manejador de interrupción es el punto de partida para el manejo de transmisión de USI I2C modo esclavo y debe configurar el contador de 4 bits a desbordamiento después de que se ha producido la transmisión de la dirección. A partir de ahí, la interrupción de desbordamiento gestiona el resto de ese mensaje de I2C y restablece el detector de condición de inicio para el siguiente mensaje.

Lea la hoja de datos

No entraré en detalle en cada uno de los pedacitos en cada uno de estos registros, pero si quieres escribir algo de código de USI es esencial que usted Lea estas secciones de la hoja de datos. Recomiendo leer el todo Universal interfaz Serial - sección USI (páginas 142-150 de la hoja de datos completa del ATTiny2313). Esto le dará toda la información que usted necesita además de lo he señalado aquí.