Paso 2: Generar el bitstream

Para este paso puedes elegir Vivado o ISE para generar el archivo de bitstream.

Aquí tienes que usar el archivo zip previamente descargado para xillinx de zedboard-eval-zedboard-1.3 c y

para xillinx de zybo-eval-zybo-1.3 c

Para esta parte hemos elegido Vivado.

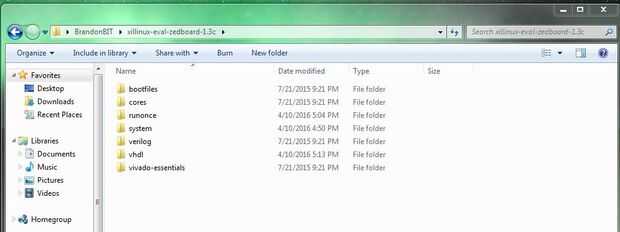

-> Crear una nueva carpeta y descomprimir xillinx-eval-zedboard-1.3 c o xillinx-eval-zybo-1.3 c

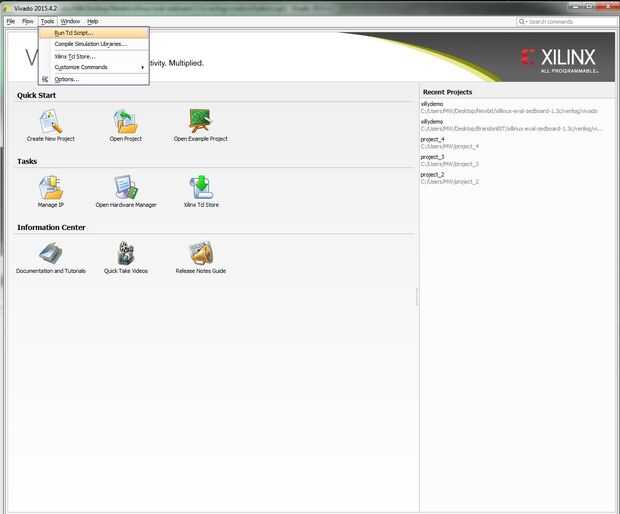

-> abrir Vivado -> Tools -> script Tcl ejecutar

-> ir en el recién creado carpeta-> carpeta de verilog y seleccione para abrir xilidemo-vivado.tcl (también puede elegir el archivo VHDL)

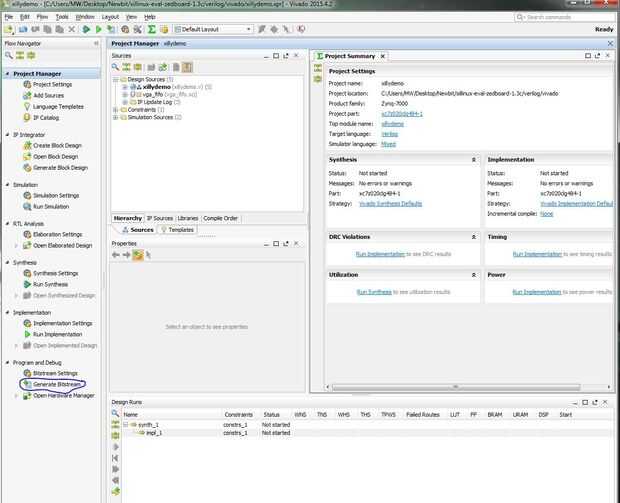

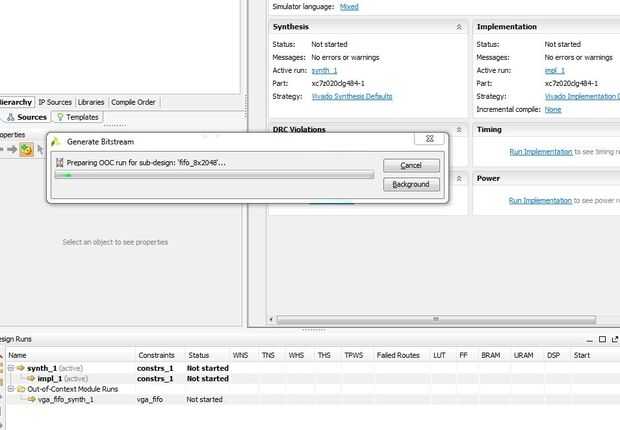

Después de la inicialización del proyecto haga clic en Generar Bitstream (a la izquierda en el navegador de flujo -> programa y depuración) y esperar a que el proceso de acabado.

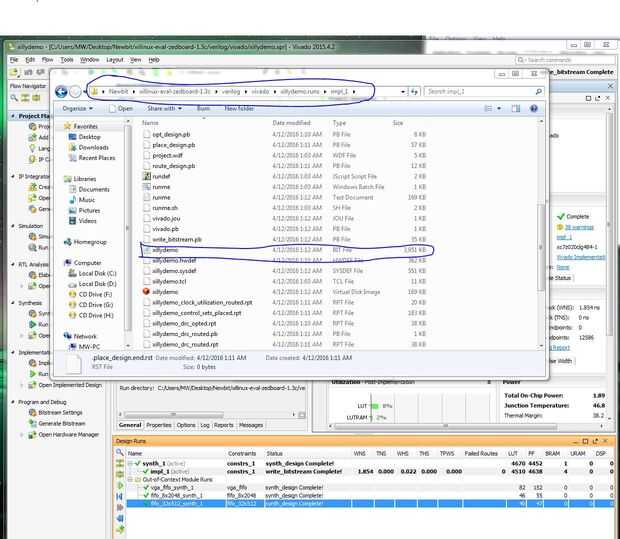

Una vez terminada la generado bitstream se encontrará en la carpeta impl_1 en la ruta de acceso Your_NewFolder\xillinux-eval-zedboard-1.3c\verilog\vivado\xillydemo.runs\impl_1