Paso 13: Matriz de Control de

T1: El contenido del contador de programa se transfiere en el registro de dirección de memoria. (Estado de la dirección)

T2: el contador de programa se incrementa en uno. (Incremento de estado)

T3: se transfiere el byte de dirección en la memoria del programa en el registro de instrucción. (Estado de memoria)

T4: depende de qué comando es ejecutado.

T5: depende de qué comando es ejecutado.

T6: depende de qué comando es ejecutado.

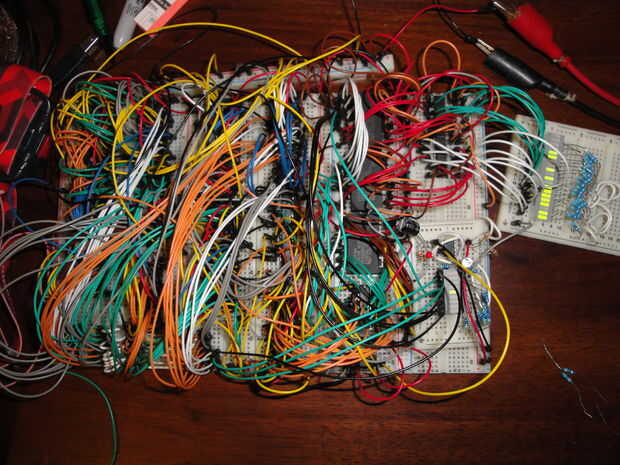

Hay dos formas principales para crear una matriz de control: usando la lógica discreta y el uso de ROM El método ROM es más fácil y más eficiente. Usando la lógica discreta consiste en diseñar un esquema de lógica masiva que es la salida de las palabras de control correcto para tu ordenador basado en un código OP de la entrada. ROM significa memoria sólo de lectura. Hay varios tipos de ROM que se puede considerar para el uso en su construcción. Para mi ordenador utilizó originalmente EEPROM (ROM programable borrable electrónicamente) pero luego cambió de puesto a NVRAM (memoria de acceso aleatorio no volátil) después la EEPROM chips ha podido escribir. No recomiendo la NVRAM como se significa memoria de acceso aleatorio y almacenamiento no permanente. EEPROM es la solución más eficiente en mi opinión.

La matriz de control tendrá tres chips de ROM cada uno con al menos 32 direcciones de almacenamiento de 8 bits (así como los elementos de calendario y contando). La palabra binario que se envía de la matriz de control se llama control ROM y contiene todos los bits de control para cada componente del ordenador. Usted quiere estar seguro organizar los bits de control y saber su orden. Ninguna operación se desea obtener una palabra de control que representa cada parte de la computadora inactiva (salvo el reloj de curso). La palabra de control para el equipo descrito en este Instructable es de 16 bits de longitud y se almacena en dos de los chips ROM de control. Las tres primeras direcciones de los chips ROM de control Mantenga las palabras de control para el ciclo de fetch. El resto de las direcciones en el chip de sostener las palabras control en pares de tres para cada código de OP. El tercer chip ROM contiene la ubicación de memoria para el comienzo de la secuencia de la palabra de control para cada código de OP y es dirigido por el propio código OP. Por ejemplo, en mi PC si le das el control el código OP 0110 dará salida binaria 21, que es la dirección del inicio de la instrucción JMP. Hay un contador de 8 bits entre la ROM de OP y el control de la ROM que cuenta de 0-2 (tres primeros estados de T) en el tercer estado T cargas la dirección outputted por la ROM de OP y cuenta desde esa posición hasta que el estado T1 borra el contador otra vez. El anillo y el contador binario para la matriz de control son controlados por una inversión del pulso de reloj para que las palabras de control están presentes cuando el creciente impulso de reloj a los elementos de la computadora. Todo el proceso en orden es el siguiente:

1.) estado T1 borra el contador a 0, la palabra de control almacenada en 0 es enviada

2.) el reloj va alta y ocurre el estado de la dirección

3.) el reloj va bajo y a su vez los incrementos del contador de control y se envía la palabra de control 1

4.) el reloj va alto y el ciclo de incremento lleva a cabo

5.) baja el reloj y los incrementos del contador de control 2, palabra de control 2 es enviado

6.) el reloj va alta y ocurre el estado de la memoria y el código OP llega en el registro de instrucción, T3 también es activo lo que significa el siguiente pulso de reloj baja se cargará la dirección de control de OP

7.) el reloj va baja y carga el contador con la dirección de la primera de las palabras de control a tres para el código dado de op.

8.) T4, T5 y T6 ejecutan el código OP

9.) T1 restablece el contador, el proceso continúa hasta que se reciba un OP de HLT. El comando HLT detiene el reloj de.