Paso 16: construcción

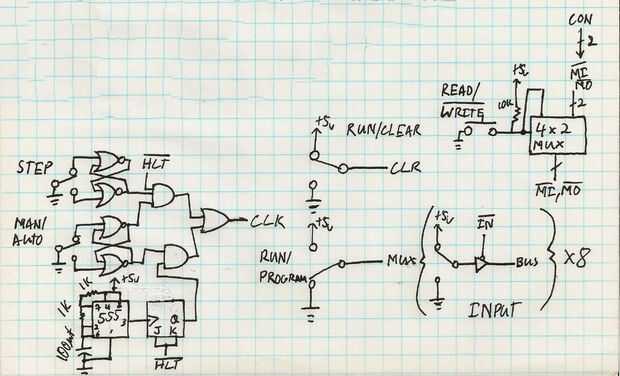

El segundo diagrama es la lógica de control para el final de la operación de la computadora. Los controles están diseñados para que cambia puede ser una entrada para el ordenador. RS_NOR pestillos se colocan delante de los interruptores a los debounce. Interruptores tienen a menudo conexiones sucias que pueden rebotar de un a un estado apagado y proporcionar más pulsos que quieras. Agregar un flip-flop a la salida de una palanca elimina los pulsos adicionales. Esto sería muy útil al usar la opción manual del reloj. No quiere el interruptor e iniciar 8 pulsos de reloj. El botón de lectura y escritura escribe el byte de entrada activado en la memoria dirigida. Cambiando la entrada por defecto control palabra RAM a dos bits RO y RI baja iniciar a escribir el ciclo. El programa de funcionamiento interruptor de cambios que entrada es activa en la dirección de memoria multiplexor. La solapa JK flop después de la 555 significa que cuando el equipo se ejecuta, no comenzará en el centro de un pulso de reloj. Una señal HLT baja detendrá el reloj de paso en el manual del reloj o 555. Y por último, el interruptor run/claro está conectado a todos los pines claro en el equipo como los de los registros y contadores.