Paso 2: Paso 2: crear un nuevo proyecto

Puedes seguir la guía consigue comenzada para crear un nuevo proyecto. Sin embargo, todavía voy por muy brevemente.

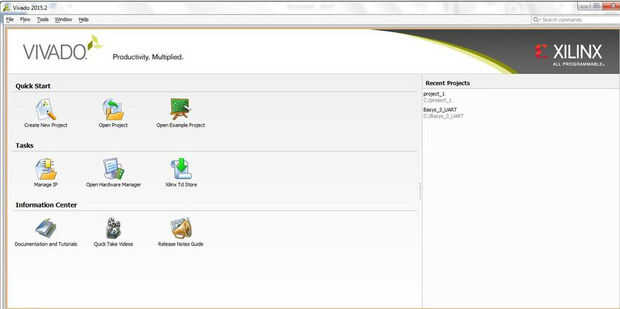

Primero, abra Vivado Webpack. Thenclick "crear proyecto nuevo"

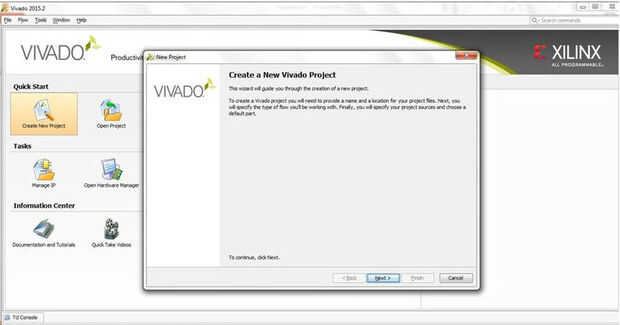

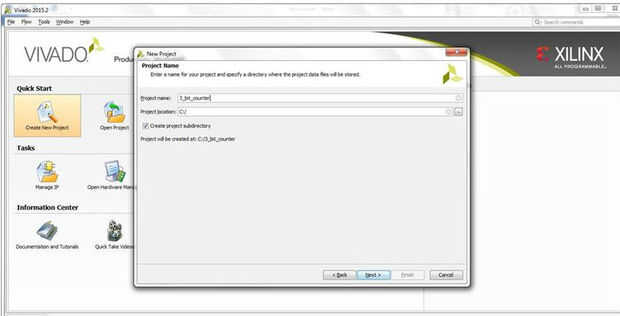

Haga clic en "Siguiente". Nombre del proyecto y elija la ubicación del proyecto. I nombre del proyecto como 3_bit_counter y puesto en mi unidad C

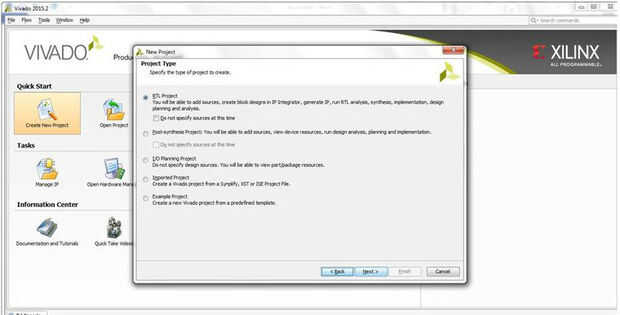

Haga clic en "Siguiente" y seleccione el proyecto. Elegimos un proyecto RTL. RTL es llamado nivel de transferencia de registro.

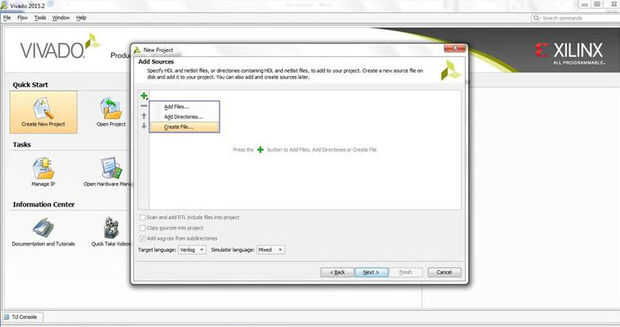

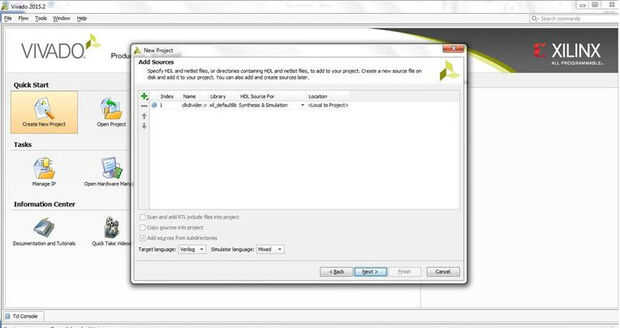

Haga clic en "Siguiente" y luego añadir fuentes. Como no tenemos ningún módulo preconstruido, tan sólo pulsamos "+" y crear archivo

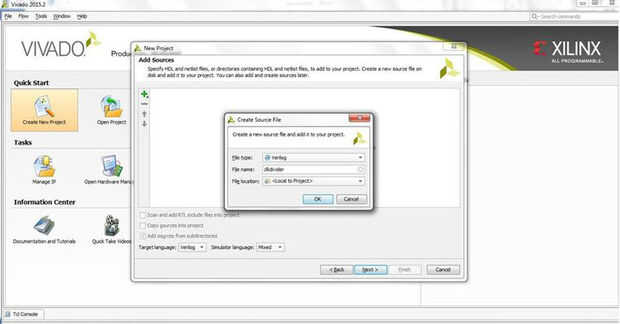

Elegir tipo de archivo Verilog y asígnele el nombre como "clkdivider". Tenemos tres módulos – divisor de reloj, contador y moudle superior. El contador y el módulo superior se creará más adelante.

Haga clic en "Aceptar" y verás que se ha creado un archivo "clkdivider"

Haga clic en "Siguiente" como no tenemos cualquier IP en el proyecto

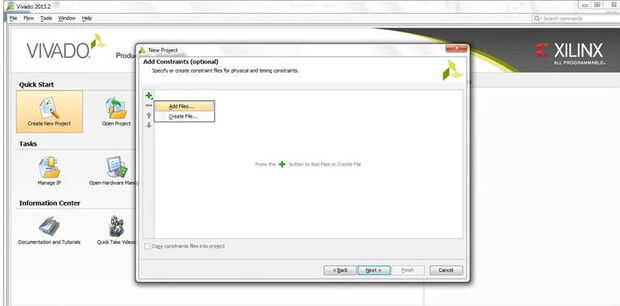

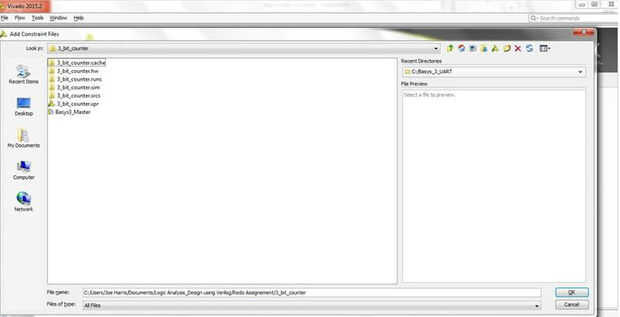

Haga clic en "+" para añadir las limitaciones en el proyecto. Puede descargar el 3 Basys xdc principal archivo de Digilent. Haga clic en "Add File" y luego averiguar donde guardar el archivo maestro xdc. En este caso, guardan en el archivo del proyecto de 3_bit_counter

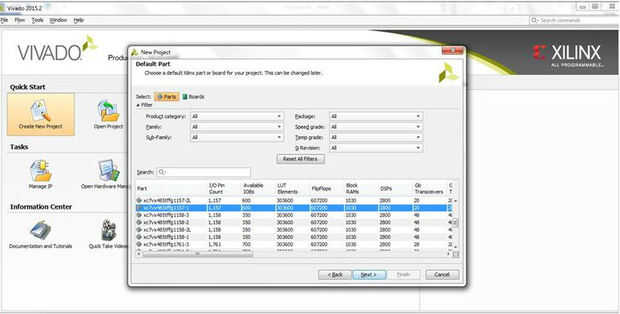

Elija el dispositivo correcto. El dispositivo FPGA Xilinx Basys 3 es Artix 7 a35T. El paquete es cpg236. El grado de temperatura es C y grado de la velocidad es -1. Puede utilizar el filtro para encontrar el dispositivo correcto.

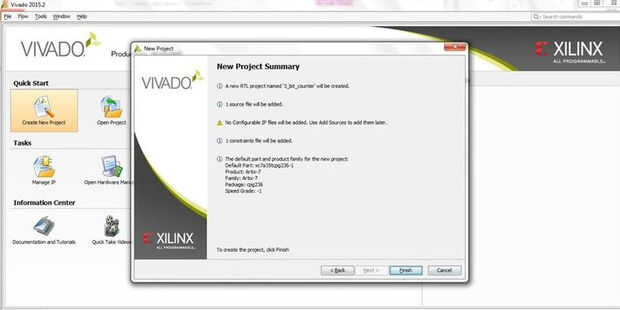

Haga clic en "Siguiente" para ver todo el Resumen de un proyecto. Si es correcta, haga clic en "Finalizar". A continuación, se crea el nuevo proyecto