Paso 4: Paso 4: crear módulo contador

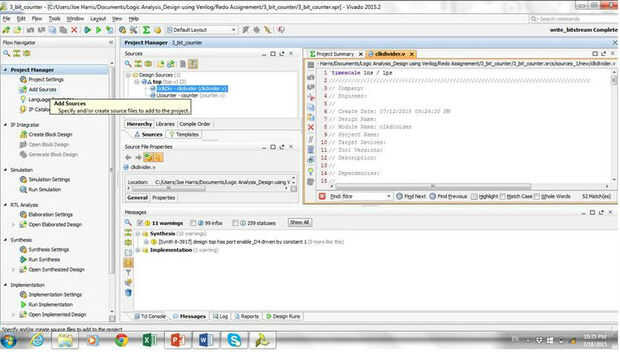

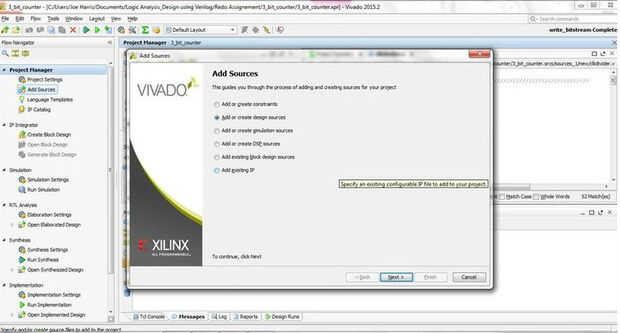

Tenemos que añadir fuentes. El navegador de flujo y haga clic en "Agregar recursos"

A continuación, seleccione "Agregar o crear recursos de diseño" y siguiente. Esto le llevará a añadir o crear ficheros de interfaz. Sólo tienes que seguir lo que hicimos en el paso 2 para crear un archivo de verilog. Puede introducir entradas o salidas. O simplemente ignorarlo y hacerlo cuando se escribe el código.

Una vez haya creado el fichero, podemos escribir la lógica del contador. La entrada es la velocidad de reloj para el contador y las salidas son 3 bits en el contador – Q1, Q2 y Q3.

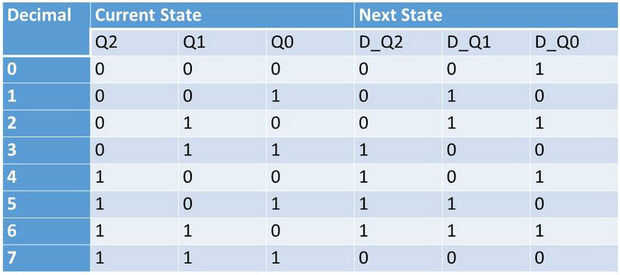

Básicamente, el contador contará de 0 a 7 en decimal (2 ^ 3 -1). Así pues, tenemos Estados actuales y próximos. El estado actual es el bit almacenado en el registro actualmente y el siguiente estado es el que se pondrá en el registro cuando el reloj alcanza el borde positivo.

El estado actual es la salida Q, mientras que nombre variables de estado siguiente D0, D1 y D2

Así, podemos describir como sigue la lógica de estado actual y siguiente. Cuando terminamos contando 7, el contador volverá a 0. (véase la tabla)

Podemos usar K-map para generar la ecuación lógica para cada bit en el estado siguiente. Entonces, utilizamos el flip-flop (función de biblioteca FDCE) para generar la salida.

Nota: puede utilizar el estado conductual para escribir la lógica del contador. Hay un ejemplo en Digilent aprender sitio: https://learn.digilentinc.com/Documents/262

Puede encontrar el código detallado con comentarios en el archivo de proyecto.