Paso 5: Paso 5: crear el módulo superior

Siga el paso 4 para agregar un módulo superior. Entonces, necesitamos definir entradas y salidas que conectan con el ambiente externo. La única entrada es el reloj de 3 Basys. Hay tres tipos de salida, enable_Dx, cx y dp. El enable_Dx es el poder de cada dígito del display de 7 segmentos. Hay 4 total 3 Basys. Sin embargo, sólo necesitamos 3. El cx es la conexión de segmentos. En cada cifra, hay siete segmentos de ca a cg. La dp es el punto decimal en la pantalla. No necesitamos usar dp en el proyecto.

Entrada:

CLK / maestro reloj Basys 3

Salidas:

enable_D1, / / derecha dígito

enable_D2

enable_D3,

enable_D4, / / izquierda dígito

CA, cb, cc, cd, ce, cf, cg / / conexiones del segmento

DP / / punto decimal

También tenemos las siguientes variables para instanciar el divisor del reloj y controlar qué tan rápido el dígito es encendido y apagado. Todas ellas son variables de red.

clkout1; interno de señales para la salida de reloj dividida

clkout2; interno de señales para la salida de reloj dividida

clkOut; interno de señales para la salida de reloj dividida

Q0, Q1, Q2; interno de señales para la salida del contador

alambre de n, o, p; interno de señales para controlar el encendido / apagado de 3 dígitos

Luego, usamos la función nivel de gate control en y fuera de la unidad. La cifra es de ánodo común. El pin de la FPGA para el dígito está conectado como salida mientras que una constante de 3, 3V se suministra como entrada en el LED. Para encender la unidad, tenemos que conducir el perno bajo (activo bajo). Puede encontrar los detalles en el manual de referencia de 3 Basys. Nunca utilizamos la izquierda más dígitos enable_D4, así que asignamos al constante 1' b1. Luego, utilizamos la y y no función de puerta para hacer la cifra y basados en el clk generado a partir de clkdivider

asignar enable_D4 = 1' b1; Apague la izquierda el dígito que es D4

y U1 (n, clkout2, clkout1); Utilice la puerta y para encender y apagar los dígitos por lo sólo un dígito está en un momento

y U2 (o, clkout2, ~ clkout1); Utilice la puerta y para encender y apagar los dígitos por lo sólo un dígito está en un momento

y U3 (p, ~ clkout2, clkout1); Utilice la puerta y para encender y apagar los dígitos por lo sólo un dígito está en un momento

no (enable_D1, n); n = clkout2 & clkout1, enable_D1 es bajo (encendido) cuando es alta clkout2 y clkout1

no (enable_D2, o); o = clkout2 & ~ clkout1, enable_D2 es baja (encendido) cuando el clkouut2 es alto y clkcout1 bajo

no (enable_D3, p); p = ~ clkout2 & clkout1, enable_D3 es bajo (encendido) cuando es baja la clkout2 y clkout1 es alta

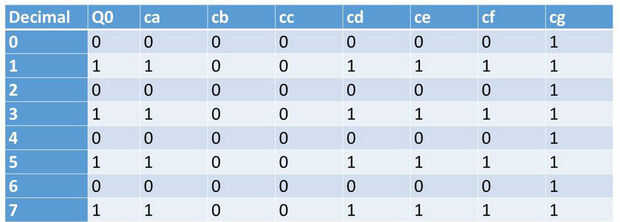

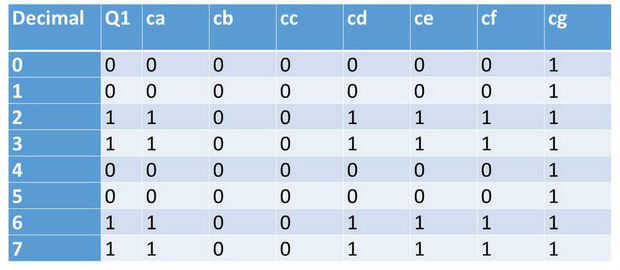

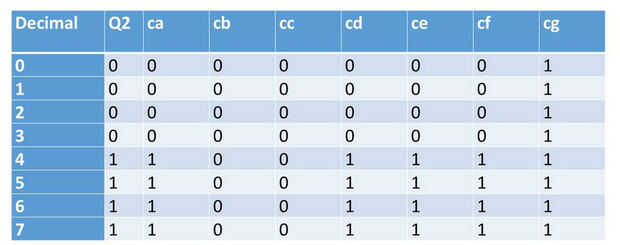

Después de eso, decidimos la lógica para el siete segmento en cada dígito. Igual que enable_Dx, cx es señal baja activa. Así que, para encender el segmento, tenemos que conducir la FPGA a la baja. Aquí están las tablas de verdad para el Qx (Q2, Q1, Q0) y ca-cg (ver tablas)

De la tabla de verdad, podemos tener la siguiente conclusión

BC y cc son siempre 0

CG es siempre 1

CA, cd, ce y cf siempre tienen la misma salida

valor de ca es evaluado por Qx

Por lo tanto, podemos tener la siguiente asignación. Para cb-cg, es bastante stragightforward. CA, usamos nido coniditional operador para evaluar la enable_Dx para decidir la salida de la ca. Si enable_D1 está activada, lo que significa la izquierda dígito (Q0) es, de la tabla de verdad, ca será Q0. De lo contrario, tenemos que evaluar la otra condición (enable_D2 está en). Si enable_D2 está activada, entonces ca es igual a Q2 y así sucesivamente.

¿asignar ca = (enable_D1 == 0)? ¿Q0: ((enable_D2==0)? ¿Q1: ((enable_D3==0)? Q2:1'b1)); Use el operador condicional

asignar cb = 1' b0; CB es siempre en

asignar cc = 1' b0; CC está siempre en

asignar cd = ca; salida de CD es igual que el ca

asignar ce = ca; salida de CE es igual que el ca

asignar cf = ca; salida de CF es igual que el ca

asignar cg = 1' b1; como sólo tenemos que tener cero o uno, así que cg es de todos los tiempos

asignar dp = 1' b1; Apagar el punto decimal

Finalmente, necesitamos crear una instancia del módulo de clkdivider y contador.

Puede encontrar el código con comentarios en el archivo de proyecto.