Contexto

Para nuestro proyecto de ingeniería, nuestros tutores quiso enfrentar los desafíos del diseño de un sistema en tiempo real con un relativamente alto rendimiento sobre los limitados recursos (memoria, ancho de banda).

Las especificaciones requieren una plataforma de juego con el siguiente hardware:

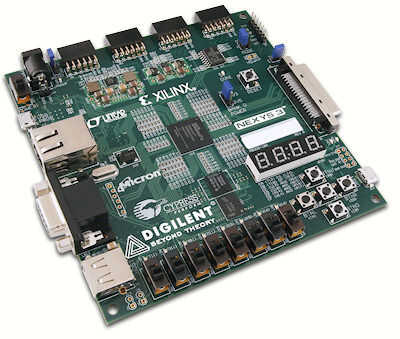

- Junta de SDMONexys 3 de Digilent (para la implementación de una GPU en el FPGA)

- Junta de MCBSTM32F400 de Keil (para el sistema operativo de la plataforma de alojamiento y almacenamiento de los datos del juego),

- un DisplayTech DT035TFT LCD con un controlador de Novatek NT39016 (pantalla de portátil de color verdadero).

Hay dos equipos de dos estudiantes que están trabajando en este proyecto, un equipo se centra en el MCU del brazo y el otro en la GPU.

Especificaciones

La plataforma tiene que coincidir con el rendimiento de una plataforma de 16 bits juegos comerciales como Super Nintendo, Sega MegaDrive, con múltiples capas y desplazamiento. La plataforma consta de dos componentes principales: la GPU y el MCU de la placa base conectado a la salida de vídeo.

- Los requisitos específicos del MCU son los gráficos API para la GPU, la API de audio para el codec de audio a bordo usuario IO, interfaz MCU/GPU, interfaz de la tarjeta SD. Programación del videojuego. Un módulo para configurar la pantalla (brillo, contraste etc.) también se considera dentro de la GPU.

- Los requisitos específicos de GPU son pantalla multicapa, la mezcla de diferentes capas con transparencia, colores de 16 bits RGBA, múltiples capas de desplazamiento, operaciones básicas 2D (bitblit (copia), relleno de color, modificación de la transparencia y su combinación (borrar, mover, etc.)), generación de primitiva (líneas, círculos, texto). LCD y VGA video salidas. Gráficos orientados a controlador de memoria con acceso a DMA.

Plan de implementación

Los dos equipos tendrán que colaborar regularmente para desarrollar los dos componentes principales mencionados anteriormente. Hemos diseñado la arquitectura general de la plataforma para este (ver el primer paso).

El equipo de gráficos comenzará mediante la implementación de módulos de exhibición video HDL y prueba videos salidas usando datos de vídeo estáticos sintetizados en la FPGA. Seguirá por la implantación e integración del controlador de memoria junto con el búfer de marco para mostrar los datos almacenados en el RAM de vídeo.

Mientras tanto se ejecutará instrucción autobús registro buscar y descifrar la unidad para facilitar el acceso para mostrar registros.

La unidad de proceso de bloque se ejecutará para proporcionar funcionamiento básico 2D de los datos de vídeo en la RAM. Después de la fase preliminar de la integración con el equipo de Motherboard, Tarjeta madre, estas funciones serán probadas y depuradas.

El equipo se procederá a la implementación del controlador DMA para permitir MCU transferir datos de vídeo desde su tarjeta SD (en lugar de herramienta Digilent Adept). Y se implementarán módulos restantes de HDL, como el generador primitivo.