Paso 1: Una arquitectura Flexible global

Nuestro equipo diseña la estructura general de la GPU

Comenzamos con una búsqueda bibliográfica en diseños comerciales o académicas para aceleración de gráficos 2D.

Los puntos de interés fueron:

- ¿Cómo se transfieren los datos de vídeo a la salida de la pantalla?

- ¿como imagen diferentes módulos de procesamiento podría funcionar en paralelo sin corromper uno al otro? ¿Cómo debe gestionarse el acceso a los datos de vídeo?

- ¿Cómo el MCU deberá configurar diferentes módulos de la GPU?

- ¿lo que debería ser el formato de píxel seleccionado para cumplir los requisitos?

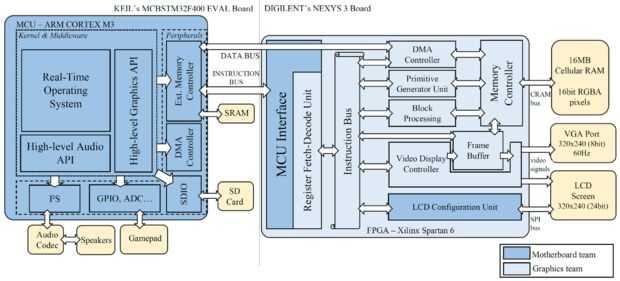

Hemos elegido una arquitectura genérica y flexible, que permite lugar para mejoras en el proyecto y lo que nos permite fácilmente agregar o quitar módulos diferentes. La arquitectura en la imagen se inspira en algunos las de existentes que mantuvieron los aspectos que parecía útil a nuestras especificaciones.

En esta arquitectura el uso de una memoria compartida de video bus y el uso de un autobús de registro unificador son los principales componentes que proporcionan gran flexibilidad para cambios en la GPU.

Para resumir los roles de los diferentes módulos, la Interfaz MCU (equipo MCU) permite el STM32 escribir en los registros de varios módulos, a través de un solo maestro, múltiples esclavos Bus de instrucciones, los datos escritos pueden configurar diferentes aspectos de la GPU o lanzar una operación de procesamiento de imágenes. Entre los módulos tenemos Regulador de exhibición de Video, que proporciona las señales de sincronización adecuado para la salida de VGA o LCD, y el Frame Buffer también se sincronizará a este módulo.

El Frame Buffer es responsable de buscar las líneas que se muestre de la memoria, aplicando alguna mezcla y desplazamiento funcionalidades y, lo más importante, es responsable de proporcionar los datos RGB correctos en el momento (sincronizado con el VDC). La obtención de la línea se realiza a través de un bus de memoria de gráficos optimizados, proporcionado por el Controlador de memoria RAM. El tamaño de píxel y resolución de la pantalla se eligen para permitir que el FB a buscar cuatro líneas en un solo horizontal esconde período (detallado más adelante), dejando el período esconde más vertical y los períodos de exhibición de imagen las operaciones de procesamiento.

Este controlador proporciona un bus de memoria compartida orientada a la prioridad que es utilizado por todos los módulos que requieren acceso al RAM. Entre los que tenemos el Bloque unidad de procesamiento, que puede operar sobre porciones de imagen rectangular, Primitiva unidad del generador, que puede generar figuras geométricas en el destino especificado y el Controlador de DMA proporciona una forma para transferir rápidamente los datos de imagen a la memoria RAM a bordo.

Y por último, LCD configuración unidad (equipo MCU) se utiliza para hacer las transferencias de datos SPI en el

Registros internos del regulador del LCD; estos registro se puede modificar para ajustar el brillo, contraste y muchas otras características de la pantalla LCD.

Con esta estructura, lograron tras principales funcionalidades:

- 16-bit RBGA Píxeles (rojo verde azul alfa) en la pantalla LCD de 24 bits, o en VGA de 8 bits,

- Frame Buffer apoyar hasta 4 capas de pantalla desplazable, independientes, configurables en tamaño,

- Completamente personalizable 16 MB RAM, pantalla direcciones de capa y sprite son definidos, por el usuario

- SRAM-como interfaz con el MCU del STM32 gracias al traductor de direcciones FSMC,

- Autobús de registro para configurar fácilmente diferentes módulos de un MCU,

- BPU: Bit blit, relleno, modificación de claro componente alpha

- PGU: primitivo generador proporcionar prixels, líneas y círculos y también los caracteres de texto,

- DMA: transferencia de datos rápidos hacia RAM para cargar texturas, sprites etc.

- LCD: puede configurar brillo, contraste, color filtrado a través de un bus SPI.