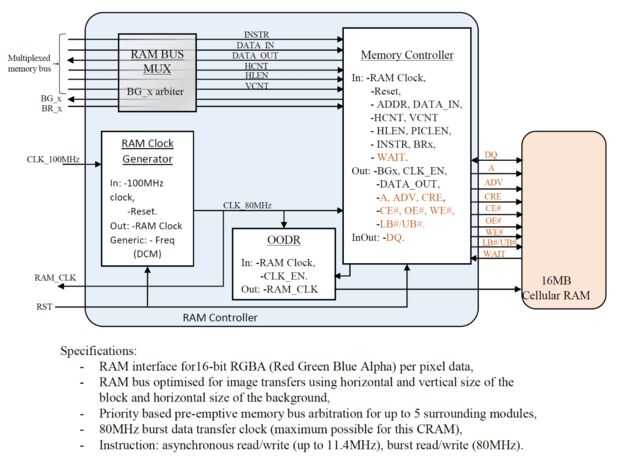

Paso 3: Controlador de memoria

La memoria RAM contiene todos los mapas de bits gráficos requeridos por los diferentes módulos de la GPU así como algunas zonas de la memoria de maniquí usados por algunos algoritmos. Es crucial que todos los módulos pueden acceder a él, cuando sea necesario, sin causar demasiada distracción entre sí. Especialmente, el frame buffer necesita acceder a la RAM periódicamente a una línea de carga de cada plano para mostrar y el momento es crítico.

Hardware gráfico especializado poseen generalmente VideoRAMs (VRAM) con varios puertos de lectura y escritura para facilitar estas cuestiones, pero el Micron de 16 MB RAM celular tiene sólo un único puerto PSRAM interfaz y es muy molesto con sus colisiones de ciclo de actualización de datos. Por lo tanto hay necesidad clara de un controlador facilitar el uso de este dispositivo y hacerlo más apto para un acelerador de gráficos.

Principales funcionalidades

El controlador de memoria proporciona ya sea:

- acceso de lectura asincrónica,

- acceso de escritura asincrónica,

- acceso de lectura de ráfaga,

- reventar el acceso de escritura.

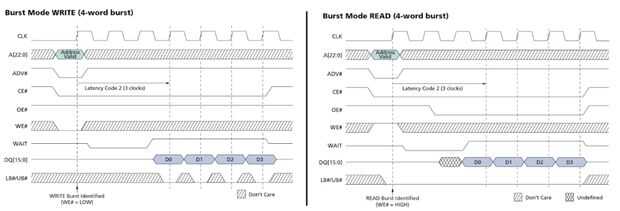

Estas instrucciones son llevadas hacia fuera generando señales tal como se especifica en la hoja de datos de la RAM del celular (ver gráficos de distribución).

Arbitraje y Bus de memoria

Hemos implementado una lógica de arbitraje preventivo bus para el bus de memoria del controlador. Esto permitiría módulos tiempo-críticos tener acceso a datos con facilidad, pero es necesario que todos los módulos de prioridad inferiores tienen que estar listos para que se Haz interrumpido durante un acceso. Puede haber hasta 5 módulos externos que pueden conectarse a esta lógica de arbitraje.

Bus de control y de datos del controlador de la RAM es compartido por los siguientes componentes (pedidos como prioridad disminuye):

- FrameBuffer;

- DMAController;

- BlockProcessingUnit

- PrimitiveGeneratorUnit

Cada uno de estos módulos está conectado al Bus de memoria del controlador de la RAM y la multiplexación del bus se realiza por la lógica de arbitraje alrededor del controlador. El bus de memoria se compone de las siguientes señales:

- INSTR [3:0]: instrucciones de la memoria

- DATA_I [15:0]: datos del módulo del RAM

- DATA_O [15:0]: datos de RAM para el módulo de

- ADDR [22:0]: dirección de la imagen, la base

- HCNT [15:0]: contador de desplazamiento horizontal,

- VCNT [15:0]: contador de desplazamiento vertical,

- PICLEN [15:0]: tamaño horizontal de la imagen,

- HLEN [15:0]: tamaño horizontal del bloque a (parte de la imagen a ser leídos/escritos),

Si INSTR es una asincrónica instrucción (lectura o escritura), entonces HCNT, VCNT, señales PICLEN y HLEN no se utilizan. Estas señales se utilizan junto con las instrucciones de descarga, para lectura y escritura de una línea o una parte rectangular de una imagen.

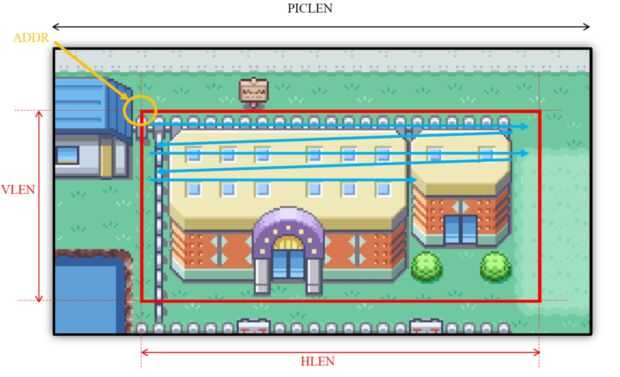

Más precisamente, durante un acceso de descarga correctamente configurado, la secuencia de acceso dirección viene dado por la siguiente fórmula:

ADDR + HCNT VCNT × PICLEN, con HCNT: 0 a HLEN − 1, VCNT: 0 a VLEN − 1

(Ver la imagen de arriba).

Este bus de memoria ciertamente complejo es necesario para asegurar la preferencia de una operación llevada a cabo por el módulo de acceso; estos contadores HCNT y VCNT permiten módulos a programar sus operaciones si consigue adelantarse o si refresco de CRAM es necesario. También permite recortar muy fácilmente de mapas de bits que es bien utilizado por la unidad de procesamiento del bloque (esto será revisado en sección BPU).

Pero debido a su complejidad, todo el componente conectado con el Bus de memoria tendrá que implementar un algoritmo bastante complejo (unos contadores, una multiplicación para comprobar colisiones de actualización). Actualmente estamos trabajando en una nueva solución basada en sincronización de búfer para simplificar la interfaz de la memoria.