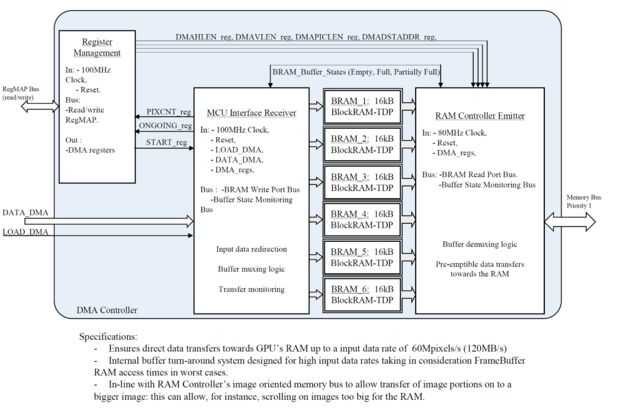

Paso 8: Acceso directo a memoria

El regulador da acceso a RAM de la GPU (el chip Micron en la Junta de SDMONexys 3) directamente desde la interfaz SRAM. Este módulo se necesitaría sobre todo para transferir datos de imagen de mapa de bits como fondo, azulejos, sprites a CRAM. Para minimizar la espera en la pantalla de carga de los juegos, tenemos que encontrar una manera de maximizar la tasa de transferencia de datos a través de este controlador.

Hemos diseñado este módulo, teniendo en cuenta la posibilidad de que la tasa de datos de entrada puede ir hasta 28MHz (en el caso donde un ciclo de escritura a la interfaz MCU ocurrió 6 relojes AHB para el STM32), pero en la práctica, debido a las señales ruidosas en la interfaz de MCU, la velocidad de datos nunca iría tan alto que (sería más probable entre 3 MHz a 10 MHz).

Además de módulo de gestión de registro, este controlador se puede separar en dos submódulos; el receptor de interfaz MCU que se encarga de supervisar estado de la transferencia y almacenamiento en búfer los datos de entrada si hay una constante transferencia DMA. El almacenamiento en búfer se realiza gracias a un total de seis 16 kB BlockRAMs, y estos tampones se reagrupan en un autobús de la única dirección en el lado del puerto de la escritura. El segundo submódulo de este controlador es el emisor de controlador de memoria RAM, este módulo se encarga de "vaciar" estas reservas escribiendo al RAM cuando están llenos de datos suficientes.

(Modos de funcionamiento detallados y límite de ancho de banda de theoritical se desarrollará aquí pronto.)

Versión parcial de programa

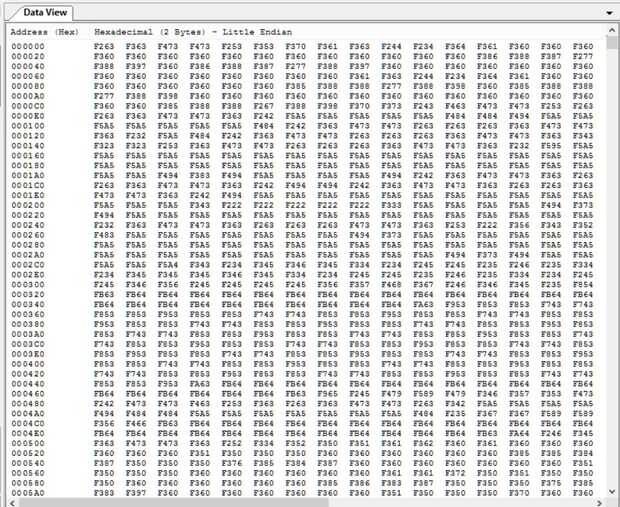

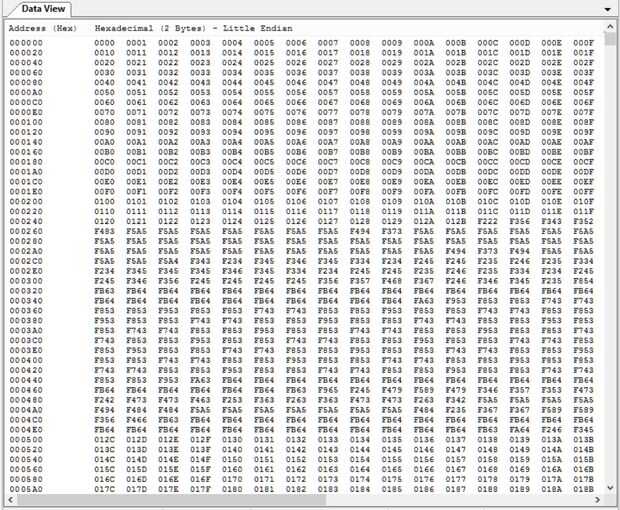

En el video, el emulador de MCU se utiliza para alimentar la salida de un contador de 16 bits como una fuente de datos entrantes de la MCU y esta información se transfiere a la zona de 300 x 200 de la capa 0. Usted puede encontrar imágenes de datos antes y después de la operación de DMA.