Paso 2: Código VHDL para el diseño y el Banco de pruebas

---Directrices de---

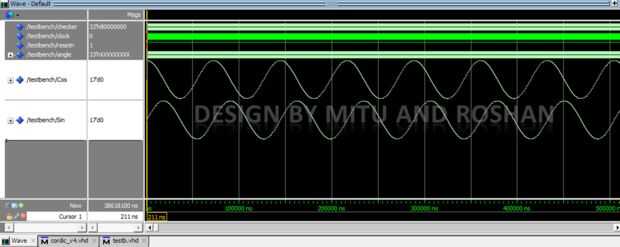

Simulación de cordic_v4.vhd - el diseño

(1) la entrada es ángulo en 32 bits + bit de signo; puede procesar cualquier ángulo de 0 a +/-360 grados con la precisión de entrada de grado 0.000000000233. Cuando dar entrada -> MSB son el bit de signo y el resto 32 bits representan la magnitud.

(2) la salida del diseño es su valor de seno y cos en 16 bits + signo bit .ie; con precisión 0.00001526. Tenga en cuenta que la salida se muestra en 2 complementan forma si el valor respectivo del seno o el cos es negativo.

Simulación de testb.vhd - Banco de prueba para el diseño

(1) después de dos pasos de simulación tire a '1' y "ejecutar todas".

(2) en simulación ventana establece la raíz de pecado y lechuga romana señales como decimales y formato > analógico (automático).

(3) zoom out para ver correctamente la forma de onda.