Paso 3: Código de Verilog para todo clasificador

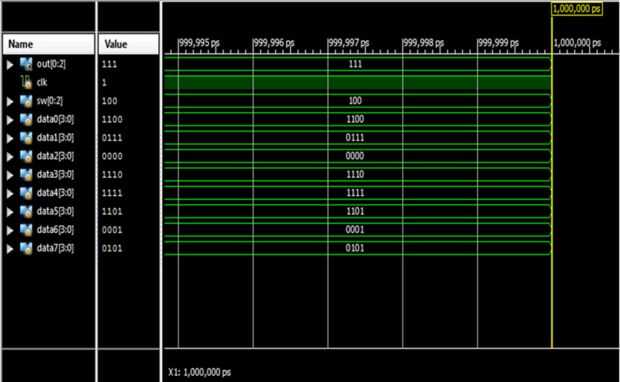

Presentado aquí, es la simulación de la máquina de clasificación toda diseñada para implementar el algoritmo. Puede verse que el RTL esquemático muestra las etapas de comparación seguidas de las calculadoras de rango seguido por el MUX para seleccionar el rango a mostrar. El módulo principal, en cada nivel de la entrada de reloj, lleva en 8 entradas y los almacena en la memoria. Entonces, el rango de cada elemento de datos es computado y alimenta a los campos de fila en la memoria utilizada. La herramienta utilizada para simular el modelo de comportamiento del circuito fue isimos con Xilinx ISE 13.2.