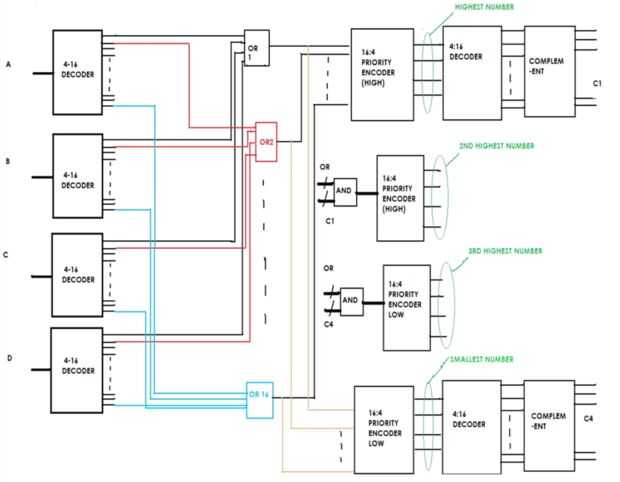

Paso 2: Descripción de Hardware

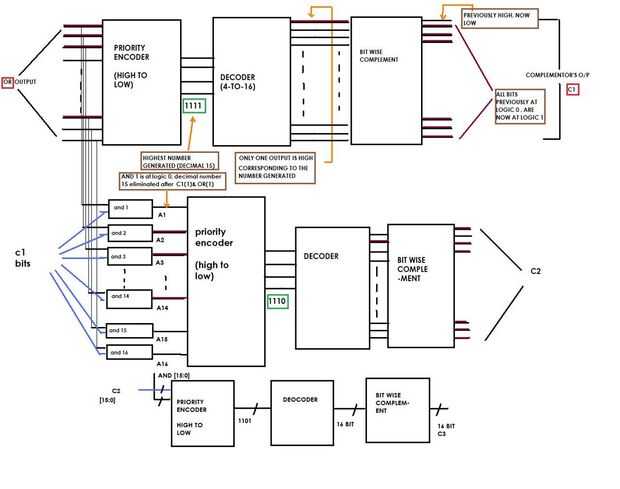

•La implementación de hardware del algoritmo de clasificación ya mencionado consta de las siguientes partes: decodificadores, circuito OR ing, codificadores de prioridad (alta-a - baja y baja a alta) y circuitos de generador siguiente prioridad. Estos componentes se suman para formar un circuito combinacional, como se muestra a continuación en la figura.

•Los circuitos de decodificador empleados se utilizan para descodificar N (bit k) número. Para cada número único del decodificador salidas que se activan. Números distintos de N, que se activan líneas distintas decodificador de N

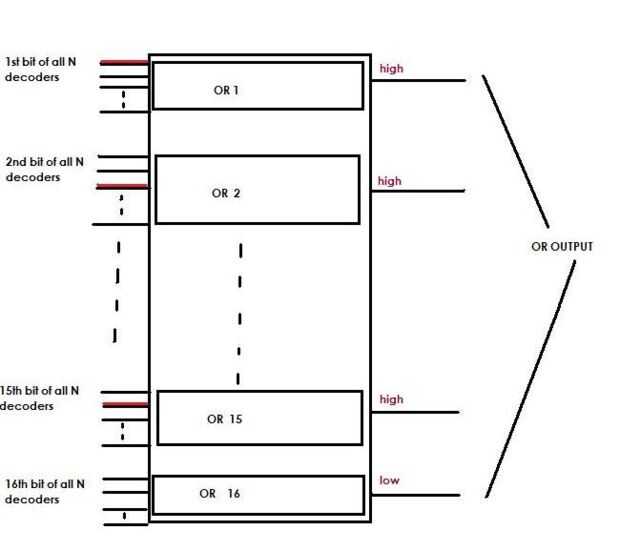

•El circuito OR-ing se compone de 2k (N-entrada) o puertas (ya k bits números se utilizan como entradas al clasificador). La broca de ith de todos se alimenta el decodificador de N a un N de entrada o puerta para conseguir el pedacito de ith del circuito OR-ing. Todos 2k bits se pueden generar de una manera similar. N líneas de salida de este circuito OR-ción será alta (lógica 1) correspondiente a un número distinto de N.

•Una vez tras obtener un ed OR señal, consta de 2 líneas de salida de k, de los cuales la salida de N líneas son altas, se emplean generadores prioritarios para generar números en un orden decreasing(increasing). Los codificadores de prioridad aquí son alta a baja prioridad o codificadores de prioridad alta a baja. Alta a baja y alta a baja prioridad codificadores son alimentados directamente con los circuitos OR-ción de la salida, generando así los más altos y los más bajos números simultáneamente. Codificadores de prioridad posteriores se alimentan de la salida del generador de prioridad siguiente.

•El siguiente prioridad de generador es un circuito que elimina un número una vez que se ha generado (sinónimo de conseguir "ranking"). Esto asegura que los números restantes consiguen volver a priorizar y logran por tanto una prioridad más alta que antes. Esto es logrado por primero descifrar el número generado, entonces poco sabio complementando la salida descodificada. Este resultado complementa es ed y con la salida de OR-ed originalmente generada. De esta manera el número que inicialmente activa el bit de ith de la salida del decodificador ya no lo hará.

•El hardware genera todos los números en un orden decreciente (de mayor a menor) que es similar a que filas.

El código de verilog para la realización del diseño de circuito se adjuntó.