Paso 2: Junta módulos

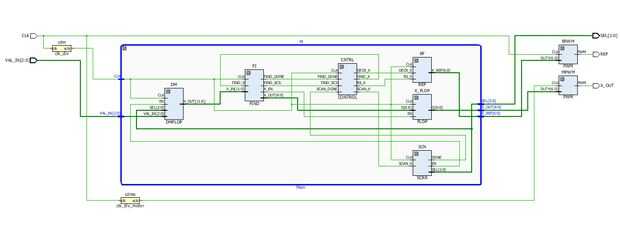

Para llevar a cabo las acciones descritas en el paso anterior, la Junta FPGA necesarios varios módulos que realizan tareas secuencialmente. Esto significó que la mayoría de los módulos tendrían que compartir la misma señal de reloj y ser programado para que operen en sincronismo. Esto se hace uniendo las entradas y salidas de varios módulos de máquina de estados finitos. Esto significa que nuestra aplicación final era mucho diferente de nuestra previsión inicial. A continuación se encuentran descripciones en detalle de lo que hace de cada módulo, así como archivos VHDL de ejemplo de los módulos, junto con algunos módulos diseñados para probar la funcionalidad del circuito.

CONTROL

El módulo de CONTROL controla las otras máquinas de estados finitos en el tablero. Esto asegura que todo está programado correctamente para que no ocurren bucles infinitos que evitan que el circuito funcione. Esto se hace por tener el bloque de control envía una señal a otro módulo (el módulo de exploración), diciéndole que haga algo. El bloque de control espera una respuesta desde el otro módulo antes de continuar. A continuación, llama el siguiente módulo (el hallazgo) una vez que reciba una respuesta para continuar el proceso. Luego, dependiendo del éxito del bloque de búsqueda, el control bloquear luego o decrementos o restablece la tensión de referencia de los comparadores. Esto asegura que los otros módulos solo realizan una acción cuando sea absolutamente necesario.

EXPLORACIÓN

El módulo de exploración es la que analiza los datos de sensor de los sensores externos. Esto logra mediante el control de la señal SEL que es salida para los muxes externa y controlando el módulo interno de DMFLOP con una señal EN y SEL. El módulo espera una señal desde el bloque de control y la exploración inicia cuando recibe. Pasa por todos los valores válidos de SEL y permite que el módulo DMFLOP que almacena los valores en un registro. Una vez que se almacenan todos los valores, devuelve una señal de listo para el bloque de control.

ENCONTRAR

El módulo de búsqueda encuentra un valor máximo del sensor de la escaneada en los datos del sensor. Una vez que reciba una señal desde el bloque CONTROL, el módulo de buscar busca un valor '1' en los valores de los sensores, que indica que el voltaje del sensor era más alto que el voltaje de referencia para que el sensor específico. Entonces salidas un valor de 7 bits que se relaciona con la posición del valor '1' en el array de datos del sensor. Si encuentra un '1', vuelve un éxito en el bloque de control. Si no 1 se encuentran en los datos, se envía una señal de falla hacia el bloque de control.

DMFLOP

El módulo DMFLOP es un registro especializado fracaso de tirón que toma una entrada del bloque de exploración EN y SEL. Utiliza estas señales para desmultiplexar las entradas de los muxes externos y almacenarlas en el registro. Este módulo es importante porque los bloques de exploración y encontrar así lo requieran para el circuito a trabajar.

PRINCIPAL

El módulo principal encapsula los módulos de CONTROL, análisis, encontrar y DMFLOP en un único módulo. Esto asegura que los módulos que todos reciben la misma señal de reloj y hace que los módulos más fáciles de incorporar a otros circuitos. El módulo principal sólo requiere una señal de reloj solo y la entrada de 3 bits de los comparadores externos. Sus salidas son la señal SEL y dos señales de obligación de 7 bits para el motor y las señales de PWM del voltaje de referencia.

REF

El módulo REF toma las salidas del módulo CONTROL para determinar lo que el valor deber 7 bits de la tensión de referencia debe ser el PWM. Es capaz de disminuir la tensión o restablecerla a su voltaje máximo, dependiendo de la salida del módulo de CONTROL.

PWM

El módulo PWM genera una señal modulada de ancho de pulso que se genera directamente a una de las salidas del tablero. El módulo toma en una señal de obligación de 7 bits que representa el ciclo de trabajo de la señal PWM. La frecuencia de la señal PWM es determinada por la señal de reloj suministrada al módulo. Este módulo se utiliza para generar el voltaje de referencia y las señales PWM motor.

CLK_DIV

El módulo CLK_DIV es un divisor de reloj. Envía una señal de reloj con una frecuencia que es igual a la frecuencia de reloj entrada dividida por un entero. El valor entero se puede cambiar cambiando un valor dentro del archivo de vhdl de divisor de reloj. Un divisor de reloj es necesario para la señal de reloj del módulo principal, así como para el módulo PWM motor. Crédito para crear el módulo CLK_DIV va a Bryan Mealy.

PRUEBA/MUX

Los módulos de prueba y MUX son pruebas de módulos del circuito.