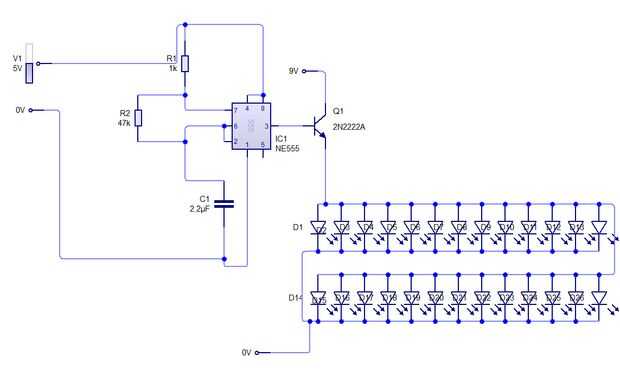

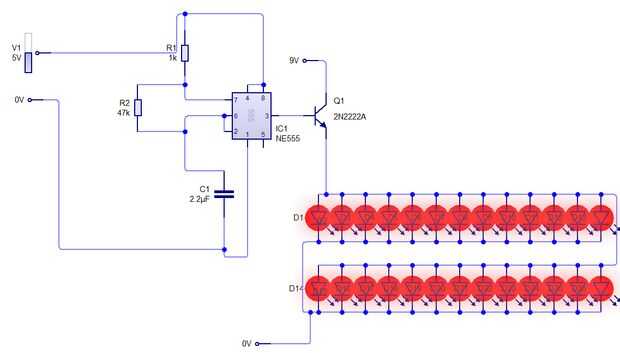

Paso 5: Diagrama del IC de temporizador NE555

Ahora qué es NE555

Ans:-

Descripción

Estos dispositivos son circuitos de cronometraje de precisión capaces de producir retardos de tiempo exacto o de oscilación. En el modo retardo o mono estable de operación, el intervalo de tiempo es controlado por una única red de resistencia y el condensador externa. En el modo de un establo de funcionamiento, la frecuencia y duty ciclo puede controlarse independientemente con dos resistores externos y un solo condensador externo. Los niveles de umbral y disparo normalmente son dos tercios y un tercio, respectivamente, de VCC. Estos niveles pueden modificarse por el uso de la terminal de voltaje del control. Cuando la entrada cae por debajo del nivel de disparo, se fija el flip-flop y la salida va alta. Si la entrada está por encima del nivel de disparo y la entrada del umbral está por encima del nivel umbral, se resetea el flip-flop y la salida es baja. El reset (RESET) de entrada puede reemplazar todas las entradas y se puede utilizar para iniciar un nuevo ciclo de tiempo. Cuando reinicio se baja, se resetea el flip-flop y la salida baja. Cuando la salida es baja, se proporciona un camino de baja impedancia entre descarga (DISCH) y la tierra. El circuito de salida es capaz de hundir o abastecimiento de corriente hasta 200 mA. Operación se especifica para fuentes de 5 V a 15 V. Con una alimentación de 5 V, los niveles de salida son compatibles con entradas TTL.

Estamos utilizando en funcionamiento Astable

Si quieres ir en detalles visita ne555