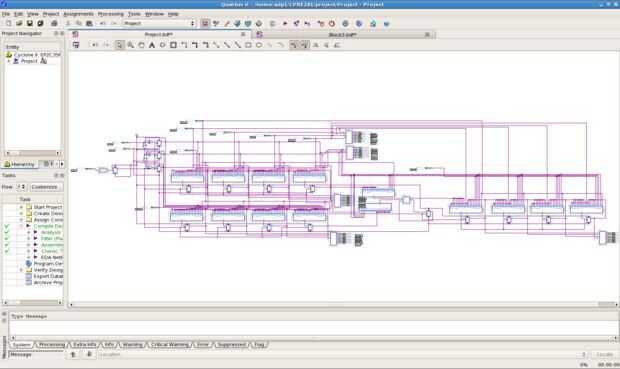

El propósito de estas instrucciones es crear un sumador de 4 bits en el Quartus II. Un sumador de 4 bits es un modelo simple de una calculadora. Tarda en dos números de 4 bits cada uno, lo que nos permite tomar números de 0-15, pero vamos a usar números del 0 al 9. Los números entonces se agregan juntos. El circuito se hace en el Quartus II y luego se programa en un campo programable Gate Array (FPGA) que permite el circuito a utilizar.

Este proyecto pretende ser para divertirse o podría ser un proyecto final para una clase, pero es sobre todo para familiarizarse con los circuitos de lógica. Este proyecto hará más sentido si ya ha tomado o está tomando una clase de lógica digital y tener un conocimiento básico de las puertas lógicas. Algunos comandos básicos de Quartus también están cubiertos si usted nunca lo ha utilizado.

El FPGA tiene botones, interruptores, LEDs y muestra número para dar cabida a la mayoría de circuitos. Quartus 2 se pueden comprar por alrededor de $3.000-$4.000; Aunque la edición web del software es libre, pero todavía requiere la compra de una FPGA. Encontré en línea FPGAs para alrededor $200. He utilizado el software de campus, asi no tengo que comprar ningún equipo. Me tomó 6 horas para completar la víbora desde cero mi primera vez. Mis esperanzas con estas instrucciones son para que puedas completar el sumador de 4 bits en menos de 5 horas. Terminación de este circuito le llevará a una mayor comprensión y cumplimiento con su complejidad.

Nota: Imágenes al principio de cada página se muestran dado pasos en el proceso. Son evitar la confusión