Paso 4: Diseño de lógica secuencial

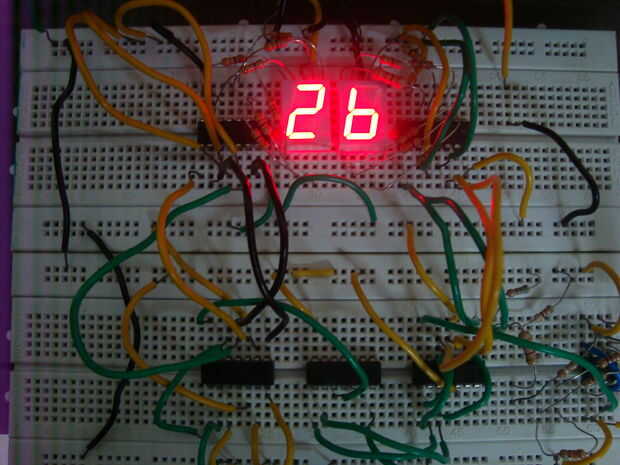

Expresiones booleanas simples como A + B o A. B' es llamados lógica combinatoria. Lógica combinatoria cuando se combina con la memoria se llama lógica secuencial. Porque permite combinaciones en secuencias o patrones recurrentes.

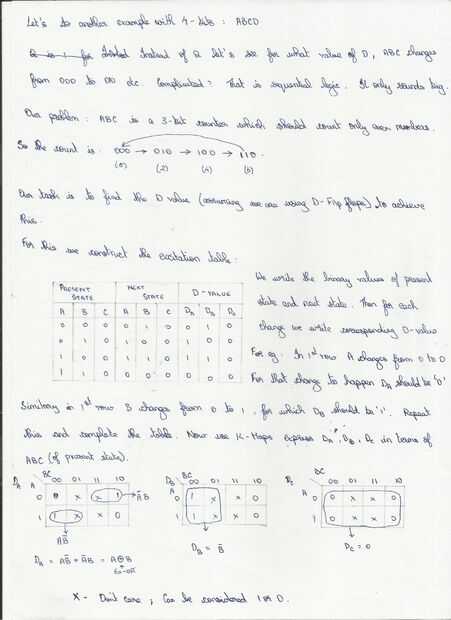

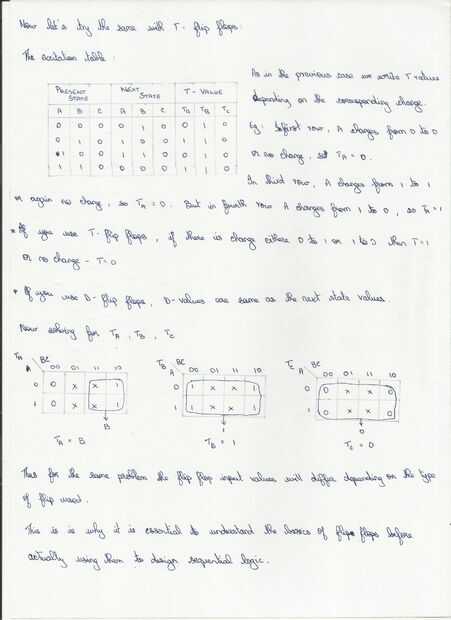

Diseño de la lógica secuencial es bastante simple si se conoce de diseño lógica de combinación - reducción de Karnaugh o mapas K (generalmente método de Quine-Mculskey no se utiliza ya que el nivel de complejidad es muy utilizado por aficionados).

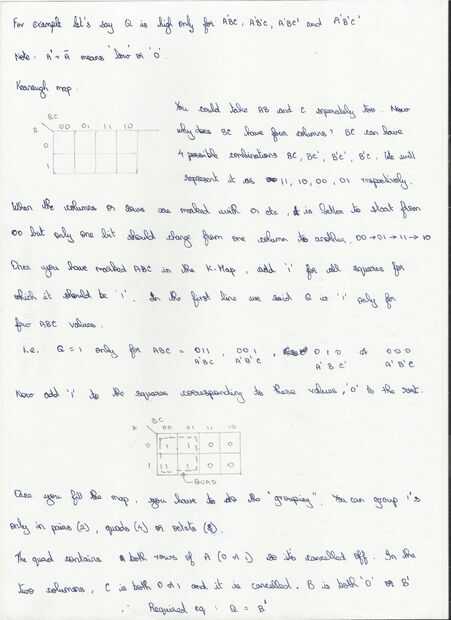

Para que se vea en cómo se realiza la simplificación del mapa de K. Sea la explicación, veamos 3 bits A, B, C. La salida Q es alta para unos valores arbitrarios de A, B, C. Ahora de esto, tenemos que formar la expresión booleana (término lujo de expresión digital) para C en términos de A, B, C. Ese es el propósito de un mapa de Karnaugh o simplemente mapas de K.

Feria de ADVERTENCIA: es casi imposible entender mapas de K al principio, pero el más verlo otra vez y otra vez se convierte en muy fácil. Cuando lo vi por primera vez fue terrible, ahora es un tiempo de paso como bingo!

Es realmente difícil hablar de mapas K y el diseño de la lógica secuencial, por lo que he subido tres mano escritas páginas. Leer a través de él. Me han hecho mi mejor esfuerzo para comprimir el contenido en 3 páginas, de lo que un libro puede ser escrito sobre!

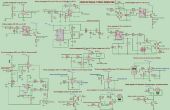

También he subido el archivo .pdf de las configuraciones de Pin del IC que utilizaremos para aplicar nuestro diseño y también nuestro circuito temporizador. Utilice como referencia o usted siempre puede buscar configuraciones de pin en el internet. Encontré este sitio útil: http://www.physics.mcmaster.ca/PHYS4DB3/Lab/Devic...