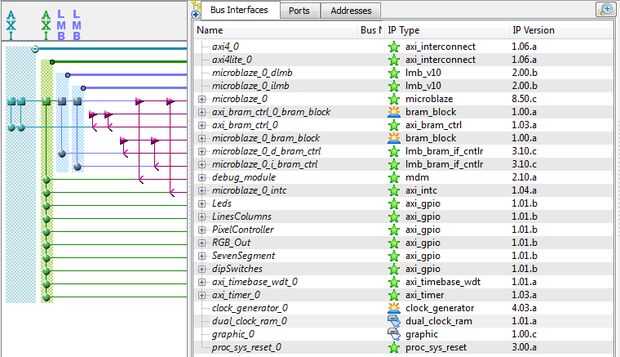

Paso 2: Diseño de arquitectura de sistema usando la herramienta XPS de EDK

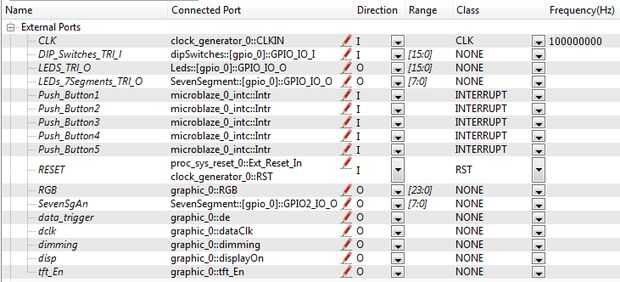

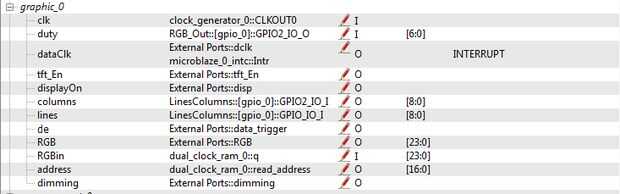

La parte principal de la arquitectura es el microcontrolador uBlaze. Está conectado con muchos periféricos GPIO para controlar LEDs, 7segmentos, imagen RAM contenido y para la lectura de interruptores DIP y de controlador de gráficos de la línea actual y la columna de depuración. UBlaze es también conectado el controlador de interrupción como un periférico. Botones de presión y temporizador interno están conectados para interrumpir el controlador.

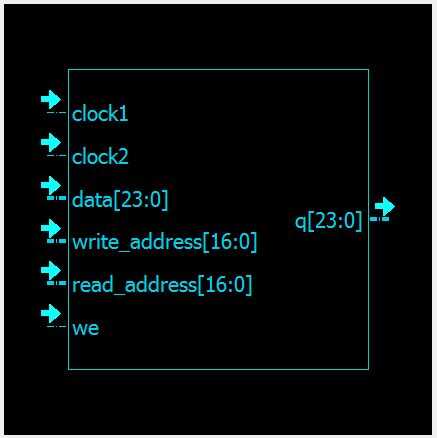

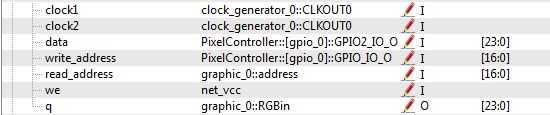

Otra parte importante de la arquitectura es la memoria RAM de la imagen. La memoria RAM es descrita por un código vhdl y es una simple memoria de RAM dual. Esta RAM contiene la imagen de controlador de gráficos se mostrará en la pantalla LCD. El tamaño de la imagen almacenado en la memoria RAM depende del tamaño virtual de la pantalla LCD. La pantalla VmodTFT tiene 272 líneas y 480 columnas y una profundidad de color de 8 bits para cada color primario. El número de células de la memoria RAM es 130560 y cada uno contiene los datos de 24 bits. Por lo tanto el tamaño de la pantalla LCD es aproximadamente 3Mb. Se requiere bloque BRAM 96 de 135 el FPGA de Artix7 ha. La memoria RAM de la imagen es interfaz con periféricos de Pixel controlador GPIO de uBlaze. Este periférico escribe en RAM el valor de cada píxel. Esto está conectada al puerto A del uBlaze. El puerto B de la memoria RAM es conectado al controlador gráfico.

La siguiente parte de la arquitectura del sistema es el controlador de gráficos. Este último accede a la imagen RAM Puerto B con la dirección de la señal y la salida del puerto B está conectada a su entrada de RGBin. El controlador de gráficos también está conectado a la VmodMIB través de los conectores Pmod para cada valor de píxel de la pantalla.