Paso 4: Crear el Custom VHDL módulos

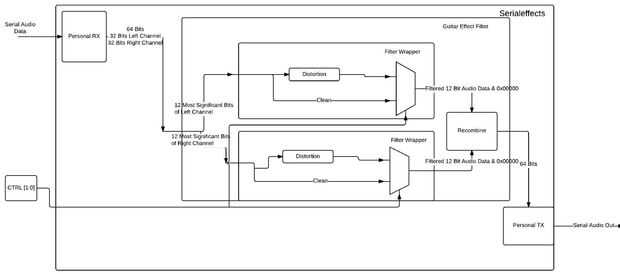

Ahora es necesario crear el código VHDL para construir una muestra de audio de 64 bits con los datos entrantes en serie desde el códec. los 64 bits representan los 32 bits de canal izquierdo y 32 bits desde el canal derecho. Esta muestra de audio entonces se divide en sus componentes derecho e izquierdos y filtrada antes de regresar a su longitud de muestra completo de 64 bits. En nuestra implementación de nuestro real audio es sólo de 12 bits de largo. Esto requiere añadir ceros a los LSBs de las muestras de audio derecha e izquierdas por separado después de la filtración y antes de volver a serializado los datos.

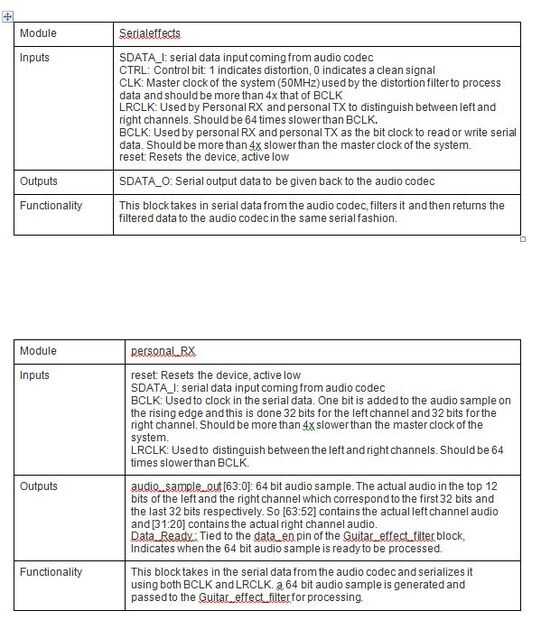

El módulo creado toma de datos en serie, la LRCLK de I2S, el BCLK I2S, un reloj de 50MHz (CLK), un reset y un pin de control para cambiar los efectos. El diagrama de bloques siguiente detalla la funcionalidad interna del SerialEffects Block.

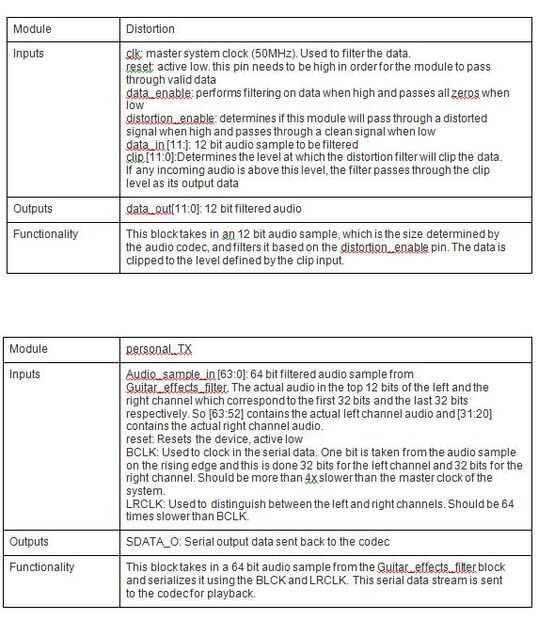

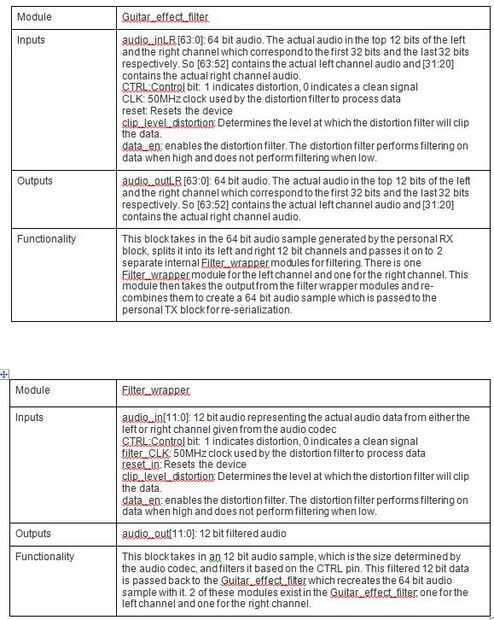

La funcionalidad de cada bloque, así como sus entradas y salidas se detallan en las figuras arriba.

LRCLK: Utilizada por Personal de RX y TX personal para distinguir entre los canales izquierdo y derecho.

BCLK: Utilizado por personal RX y TX personal como el reloj de bit para leer o escribir datos en serie CLK: 50MHz utilizado por el filtro de distorsión para procesar los datos.

El código para estos módulos se da abajo. Use el zip serialIP adjunto a la incluida en la carpeta original para el bloque de IP de serialIP.