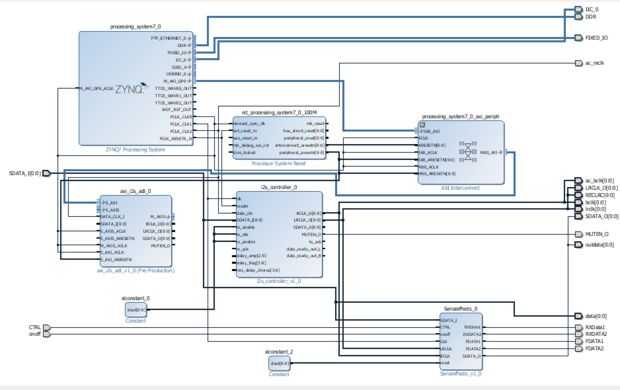

Paso 7: Ejecutar conexión automatización y IP conectar bloques

Haga clic derecho en la ventana de diseño del bloque y seleccione la opción ADD IP. Añadir la IP personalizada i2s_controller_v1_0 y SerialEffects_v1_0. Ejecute la herramienta ejecutar bloque automatización que debe estar en la etiqueta verde sobre la ventana de diseño de bloque. Ahora Conecte el FLCK_CLK1 a la entrada de clk en IP block i2s_controller_v1_0 y entrada CLK en el bloque IP SerialEffects_v1_0. Conectar el FLCK_CLK2 a la entrada de data_clk en i2s_controller_v1_0 del bloque IP. Agregar el bloque de IP llamado "const" para el diseño de bloques. Conecte la salida del bloque IP const entradas tx_enable, tx_stb y tx_enable en la i2s_controller_v1_0 de bloqueo IP. Añadir otro bloque IP const, cambie el valor constante a 0 del bloque de IP haciendo doble clic sobre el bloque de IP y luego conecte la salida del bloque de IP al pin de reset en el bloque de IP de SerialEffects_v1_0. Ahora haga clic derecho sobre todos los otros pines en el bloque de IP de SerialEffects_v1_0 y seleccione hacer externo. Esto crea puertos externos CTRL, onoff, SDATA_O y SDATA_I. Conecte un cable de SDATA_I en i2s_controller_v1_0 con el conector externo de SDATA_I. Para el i2s_controller_v1_0 crear externos para pernos de BLCK_O, LRCLK_O y MUTEN_O. Ahora para el sistema de procesamiento de ZYNQ7 haga clic en el pin de salida IIC_0 y hacer un externo. Esto debe crear una salida de IIC_0. También click derecho sobre un espacio en blanco en la ventana de diseño de bloque, seleccione crea un puerto y crea un pin de salida llamado ac_mclk. Crear otro puerto de salida y asígnele el nombre RECLRC. Conecte el pin de salida de ac_mclk a FCLK_CLK2 y RECLRC pin de salida a LRCLK. Al completar todos los pasos anteriores el diseño de bloque sería muy similar a la figura de arriba. Por favor ignorar IP bloques axi_i2s_adi_v1_0 salida patillas y RXData1, RXDATA2, FDATA1, FDATA2, outdata.