Paso 3: Los módulos de FPGA

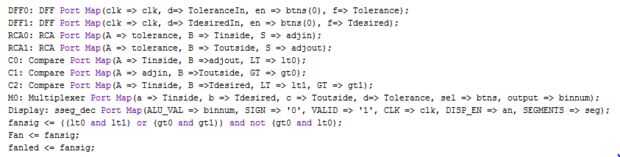

DFF: Este proyecto utiliza 2 8 bits D-Flip Flops, utilizado para almacenar la temperatura deseada y la tolerancia. Esto permite al usuario configurar sus interruptores a una nueva posición sin causar comportamiento esporádico en el ventilador. El DFF tiene 3 entradas: clk (reloj), d (7 p 0) (valor de entrada), en (enable); y 1 salida: f (7 p 0) (valor de salida). Sobre el flanco ascendente del reloj, si la entrada enable es alta, entonces el DFF establece el valor de salida al valor actual de entrada.

RCA: Este proyecto utiliza 2 8 bits ondulación llevan serpientes, se usa para ajustar las temperaturas de entrada por la cantidad de tolerancia especificada por el usuario. El RCA tiene 2 entradas: una (7 p 0), B (7 p 0); y 1 salida: S(7 downto 0) (suma). El TDAH completo de usos 7 de RCA y 1 medio sumador para agregar los dos valores de entrada comparando sus bits de magnitud misma, resultando en una suma que representa los números de entrada se suman.

Comparador: Este proyecto utiliza 3 comparadores de 8 bits, utilizados para detectar el estado actual de la balanza de temperatura. El comparador tiene 2 entradas: una (7 p 0), B (7 p 0); y 2 salidas: LT (menor que), GT (mayor que). El comparador generará una alta lt si AB es verdad.

Multiplexor: Este proyecto utiliza un multiplexor de 8 bits elegir lo que debe mostrarse en la pantalla de siete segmentos, con un una caliente señal seleccione codificada. El multiplexor tiene 4 entradas: una (7 p 0), B (7 p 0), C (7 p 0), D (7 p 0); 1 Seleccione señal: sel (4 p 0); y 1 salida: out (p 7 0). Las salidas del multiplexor: D cuando 4 Seleccione bit es alto, C 3 Seleccione bit es alto, B cuando la 2ª selecciona bit es alto, cuando la 1ª seleccione bit es alto y x "00" el resto del tiempo.

sseg_dec: Este proyecto utiliza un decodificador de siete segmentos, para mostrar información al usuario acerca de los valores actuales de la temperatura y los ajustes de los valores binarios almacenados en decimal fácilmente legible. La sseg_dec tiene 4 entradas: ALU_VAL(7 downto 0) (entrada número binario), signo (firmado), válido, CLK (reloj); y 2 salidas: DISP_EN(3 downto 0) (ánodos) de dígitos, SEGMENTS(7 downto 0). Este módulo fue proporcionada por nuestro instructor en el laboratorio y fue hecho por Bryan Mealy. En nuestro proyecto hemos utilizado números sin signo, para que muestra fue fijada a '0' y válido a '1'. Normalmente, el número binario de entrada se convierte en decimal codificado en binario, y luego los segmentos correcto y ánodos de dígitos están apagados, sin embargo para este proyecto que hemos cambiado la pantalla para ser completamente apagado si el número binario de entrada fue 0 conservar energía debe no hay nada que se muestre.

Si desea realizar cambios en el programa, el código fuente se enumera a continuación.