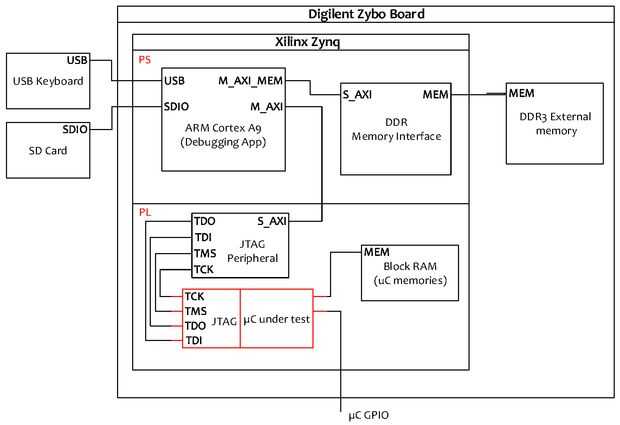

Es una herramienta basada en una tabla ZYBO que permite probar y depurar de diseños de microprocesadores. Prueba se hace en hardware, no software. Por lo tanto, los resultados son mucho más confiables. Llena el orificio en el flujo de diseño de hardware entre el software de simulación del diseño y la implementación física. El diseñador será capaz de implementar y probar su diseño en la parte de la PL de la Junta, mientras que también elegir el código que será ejecutado y establecer puntos de interrupción en él a través de la aplicación que se ejecuta en el brazo. Después de ella ejecuta el código y ver en una pantalla los diferentes registros de interés (relojes), establecida previamente en la aplicación, y cómo evolucionan. Es posible gracias a una bien preparada infraestructura que permite que cada uno hacer su propio diseño en una manera rápida y cómoda, centrándose en la operación del dispositivo y las capacidades de depuración.

¿Cómo se utiliza?

G-ICE interfaces con una aplicación que se ejecuta en el procesador del brazo. Con esta aplicación, es posible depurar y controlar el estado del procesador bajo prueba.

G-ICE se implementa en un tablero ZYBO, que permite la fase de diseño se divide en dos partes principales:

El primero es el software que se ejecuta en el procesador del brazo. Su función es permitir al usuario seleccionar un diseño de microcontrolador que quiere probar y el código se ejecute, además a establecer puntos de interrupción, relojes a registros o modos (modo de paso a paso o normal, en la que el código se ejecutará a una velocidad de reloj fijo). Durante la ejecución, los valores de todos los registros estarán disponibles para el usuario.

La segunda es la lógica programable, y en particular el interfaz JTAG implementado en él. Esta interfaz permite la U.U.T. (en este caso, el microcontrolador bajo prueba) para comunicarse con el software que se ejecuta en el procesador del brazo vía JTAG. Esto garantiza una reutilización de código total, ya que hielo G será compatible con cada diseño que implementa JTAG.

Principales ventajas

Fiabilidad:

El diseño no necesita ser probado en el software. Así, tomando el ASIC diseño y portarlo a G-ICE, el usuario será capaz de conseguir una emulación realista y valores de salida.

Velocidad:

G-ICE reduce considerablemente el tiempo de prueba de un dispositivo debido a la infraestructura de pruebas que ofrece. El diseñador sólo tiene que incluir todos los registros solicitados a la cadena de exploración de frontera y proporcionar una descripción de la cadena JTAG para la interfaz JTAG. G-ICE proporciona un completo trabajo entorno de depuración sin esfuerzo.

Cómodo y portátil:

G-ICE es una herramienta independiente que necesita sólo una pantalla de PC y una fuente de alimentación para trabajar. Esto hace innecesario equipamiento adicional, situado generalmente en un laboratorio o un sector especial de la empresa o Universidad, por lo que es posible para el diseñador a trabajar casi en cualquier lugar.

Archivos de código fuente: