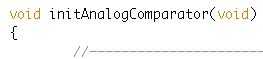

Paso 12: Configuración de comparador analógico

void initAnalogComparator(void)

{

//---------------------------------------------------------------------

Configuración de ACSR

//---------------------------------------------------------------------

Cuando este bit se escribe lógica, el poder de lo analógico

Comparador esté apagado. Este bit se puede establecer en cualquier momento para activar

desactivar el comparador analógico. Esto reducirá el consumo de energía en

Activo y el modo de espera. Al cambiar la broca de la ACD, el análogo

Interrupción del comparador debe estar desactivada despejando la ACIE en

ACSR. De lo contrario puede ocurrir una interrupción cuando se cambia el bit.

CBI(ACSR,ACD);

Cuando este bit está establecido, una tensión de referencia fija bandgap reemplaza la

entrada positiva del comparador analógico. Cuando este bit se borra,

AIN0 se aplica a la entrada positiva del comparador analógico. Cuando

referance de la banda prohibida se utiliza como entrada para el comparador analógico, se

llevará un cierto tiempo para estabilizar la tensión. Si no se

estabilizado, la primera conversión puede dar un valor incorrecto.

CBI(ACSR,ACBG);

Cuando la ACIE bit se escribe lógica uno y el bit en el estado

Registro se encuentra, se activa la interrupción del comparador analógico.

Cuando escrito lógica cero, se deshabilita la interrupción.

CBI(ACSR,ACIE);

Cuando la lógica escrito uno, este bit permite la función de captura de entrada

en temporizador/Counter1 mediante el comparador analógico. El

salida de comparador en este caso se conecta directamente a la entrada

captura lógica de front-end, haciendo la comparación utilizan el ruido

supresor y borde de seleccionan características de la entrada del temporizador/Counter1

Captura de interrupción. Cuando escrito lógica cero, no hay conexión entre

el comparador analógico y la función de captura de entrada existe. Para

hacer el comparador activar la captura de entrada del temporizador/Counter1

interrupción, el bit ICIE1 en el registro de máscara de interrupción de Timer

(TIMSK1) se debe establecer.

CBI(ACSR,ACIC);

Estos bits determinan que eventos de comparador que desencadenan la analógica

Interrupción del comparador.

ACIS1 Modo de ACIS0

0 0 palanca

0 1 reservado

1 borde cae 0

1 1 borde de levantamiento

SBI(ACSR,ACIS1);

SBI(ACSR,ACIS0);

//---------------------------------------------------------------------

Configuración de DIDR1

//---------------------------------------------------------------------

Cuando este bit se escribe lógica uno, el digital entrada de buffer de la

Pin de AIN1/0 está desactivada. El bit correspondiente del registro PIN será

siempre se lee como cero cuando este bit está establecido. Cuando una señal analógica es

aplicado al pin AIN1/0 y la digital entrada de este pin no es

es necesario, este bit se debe escribir lógica uno para reducir la energía

consumo en el búfer de entrada digital.

SBI(DIDR1,AIN1D);

SBI(DIDR1,AIN0D);

}