Paso 1: Usando el mundo arquitectura VHDL

En primer lugar, obtenga e instale Vivado webpack:

- Ir a http://www.xilinx.com/support/download.html

- Ir a Vivado y sdk independiente web instalar cliente

- Seleccione su sistema operativo

- Descargar el archivo

- Instalar Vivado webpack y el SDK siguiendo las instrucciones

Luego, descargar el diseño del sistema de base de la tarjeta y usar con Vivado:

En este ejemplo, usaremos el ZYBO de Digilent.

- Ir a https://www.digilentinc.com/Products/Detail.cfm?P...

- Descargar el diseño del sistema de la Base de ZYBO

- Extraer el archivo

- Lanzamiento de Vivado

- Haga clic en abrir el archivo

- Abra el archivo zybo_bsd.xpr que está en la carpeta: zybo_base_system\source\vivado\hw\zybo_bsd

- Seleccione actualiza automáticamente a la versión actual (si se ofrece)

- Luego haga clic en Informe IP estado y elija actualizar seleccionado y OK

- Cerrar la ventana de advertencia (no preocuparse) y vaya a herramientas/crear y paquetes IP

Crear la dirección IP para el mundo:

Ahora usaremos al empaquetador IP de Vivado para insertar el mundo como una IP en el sistema mundial.

- Cuando veas la ventana superior usted tiene que haga clic en siguiente y luego crear un nuevo AXI4 periférica

- Nombre luego el periférico que quieras (puedes añadir una breve descripción)

- Para la interfaz AXI tienes que dejar el nombre S00_AXI y seleccione el tipo de Lite y el modo esclavo. Anchura de los datos debe ser 32 y el resto no importa

- Finalmente puede haga clic en siguiente y seleccione Editar IP termine

Integrar el código en el IP:

Ahora tenemos el empaquetador IP abierto; Insertamos el código fuente en esta IP en orden al sistema correcto.

- Primero descargar el archivo

- Eliminar el archivo en la dirección IP e importar el archivo de la carpeta de archivo (clic derecho/añadir fuentes/crear o agregar fuente de diseño)

- Haga clic en la ficha paquete IP y todo lo que pide para cada parte hacer y finalmente haga clic en nuevo paquete IP

- Usted está ahora a la ventana principal de Vivado

- Hacer un clic derecho en el diagrama y elija Agregar IP y seleccione tu IP (tu IP se añade al sistema que tienes que conectar tu IP)

- Para todos los puertos externos (LED0-5, PWM_OUT y INFRA_SENSOR) do derecho haga clic en él y elija hacer externos (tendrá ahora todo el puerto externo del mundo creado)

- Luego haga doble clic en la interconexión de AXI y añada uno amo interfaz

- Ahora conecte este nuevo maestro interfaz para su S00_AXI

- Luego conecte M08_ACLK y M08_ARESETN a otro

- Conecte su s00_axi_aclk y s00_axi_aresetn a la anterior

- En la ficha Editor de dirección y derecho haga clic en su dirección IP y seleccione Auto asignar dirección

- En la pestaña de fuentes haga clic derecho sobre el system_i y seleccione generar salida productos

- Haga clic de nuevo en él y seleccione crear contenedor de HDL

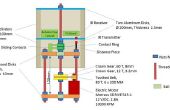

- Finalmente actualizar el base.xdc de archivo de restricción (las siguientes imágenes es un ejemplo)

- Ahora puede generar el Bitstream

Generar la FSBL:

Ahora tienes la system_wrapper.bit generado. Ahora generaremos el archivo FSBL.

- Al final de la generación del Bitstream aparece una ventana: cerrar e ir a archivo/Exportar/exportar hardware y seleccionar incluyen flujo de bits y haga clic en OK

- Ir a archivo/lanzamiento SDK (y seguir los pasos)

- Lanza el SDK de ir a File/New/Board Support Package y haga clic en finalizar y luego seleccionar la biblioteca xilffs, xilrsa y xilmfs y luego OK

- Ir a proyecto de aplicación de nuevo de archivo le dan un clic nombre en uso existentes (seleccione el paquete de la placa que acaba de crear) y en siguiente

- Se genera el FSBL!

Si usted tiene alguna dificultad durante el proceso, debería ver el pdf que muestra unas fotos para ayudarte.