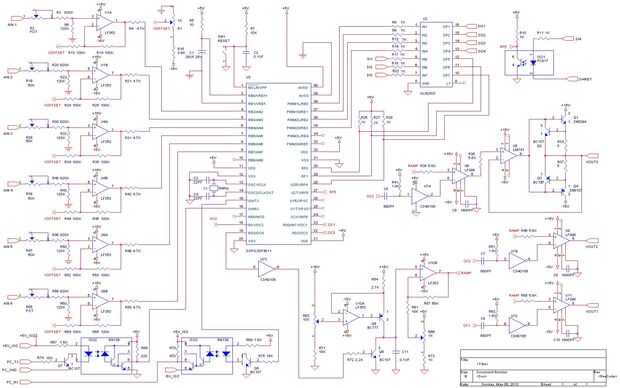

Paso 13: Diagrama del circuito y las funciones

El general circuito esquemático se muestra en la figura. La versión de tamaño completo puede verse haciendo clic sobre la imagen y si es necesario descargar el archivo grande. Una versión impresa de dos páginas también se da en el paso de la fabricación junto con los archivos del PCB 1:1.

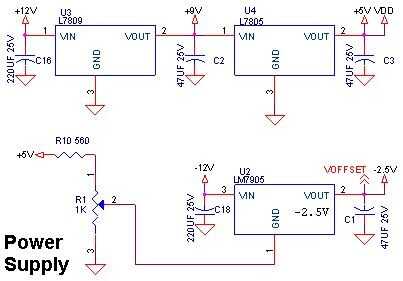

Fuente de alimentación:

La fuente de alimentación se deriva de la ±12V y + 5V salidas de la SMPS de PC que están protegidos por 250mA y 500mA fusibles respectivamente.

U3 provee 9V de + 12V y U4 + 5V desde los + 9V.

R1 se ajusta la tensión de contacto 1 de U2 que es alimentado por - 12V para proporcionar un - 2.5V offset voltaje para las etapas de entrada analógicas.

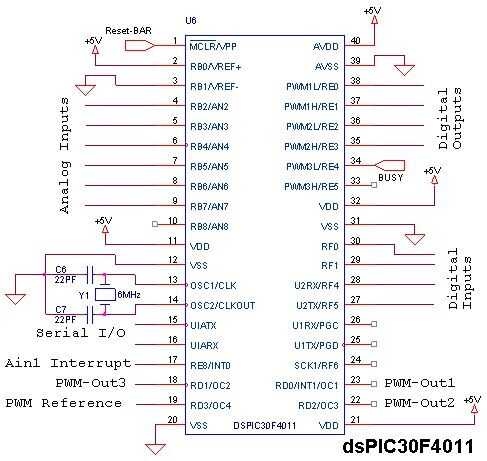

DSPIC30F4011 circuito:

La interconexión básica del DSPIC30F4011 micro-controlador se muestra en la figura.

+ 5V forma la VDD / AVDD y Gnd el VSS, una versión filtrada de + 5V formas el + VREF.

Los pernos 4-9 AN2-AN8 forma los seis canales de entrada analógicos.

Pines 13 y 14 están conectados con el cristal de 6MHz.

Pines 15 y 16 se utilizan para la comunicación serial

Pin 19 OC4 es la referencia PWM para la toma de muestras – DAC

Pasadores de 23, 22 y 18 forman las salidas PWM DAC

Pernos de 27-30 son las entradas digitales

Pernos de 35-38 son las salidas digitales

Pin 34 se utiliza para indicar la disponibilidad

Pines 25 y 26 están reservados para la programación serial

Y Pin 17 es usado como la interrupción de disparo de borde para el canal de entrada analógica 1

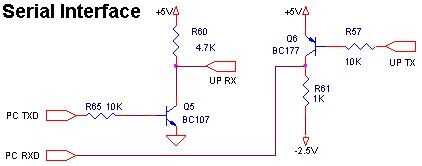

Interfaz en serie:

Una simple interfaz se basa en la disponibilidad de + 5V y - 2.5V proporciona. Q5 forma un inversor y convertidor de nivel de TTL para el PC TX datos y Q6 toma el microcontrolador TTL TX datos y convierte en pseudo RS232 niveles de - 2, 5V a + 5V adecuado para los datos de RX del PC.

La tarifa de datos programada en el software es de 115 KBPS.

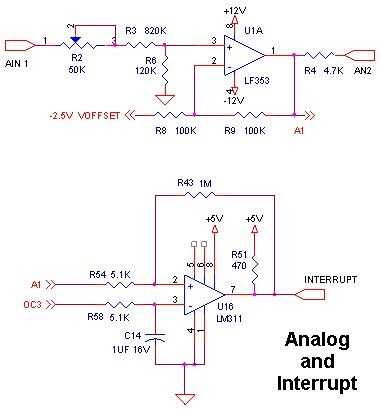

Interfaz analógica:

U1A forma la interfaz de entrada del canal analógico 1. El divisor potencial R2 + R3 y R6 crea una impedancia de entrada ~ 1MΩ y dividir por 8 para la entrada de ±10V señal. La señal dividida potencial aparece en la salida de U1A con una ganancia de no invertir de 2.

A - 2, 5V voltaje compensado se alimenta en el R8 que aparece como un + 2.5V offset en la salida de U1A debido a la unidad de inversión ganar R8/R9.

Efectivamente la señal de entrada de ±10V aparece como un 0 a + 5V señal en AN2. La impedancia de entrada es ~ 1MΩ y la respuesta de frecuencia determinada por las características de gran ancho de banda FET OpAmp LF353 es típicamente 2 MHz.

Interrumpir el circuito:

La salida de U1A forma una de las entradas para el comparador IC U16, LM311. La otra entrada está formada por un promedio del PWM salida OC3. U16 está configurado como un comparador con histéresis usando el resistor de retroalimentación R43.

En funcionamiento el modo de interrupción se invoca por software durante las funciones del modo de captura continua y correderas. La salida de U1A se compara con el valor medio de OC3 que miente entre 0 y + 5V y una forma de onda rectangular se genera en la interrupción de la entrada. Esta interrupción se utiliza para seleccionar el + ive / ive - borde para activar el modo de captura.

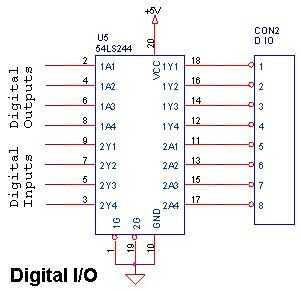

Interfaz de entrada/salida digital

Un Buffer Octal 54LS244, U5 se utiliza para amortiguar las entradas digitales y salidas hacia y desde el microcontrolador. Esto proporciona amortiguación y protección a los pins de I/O del microcontrolador.

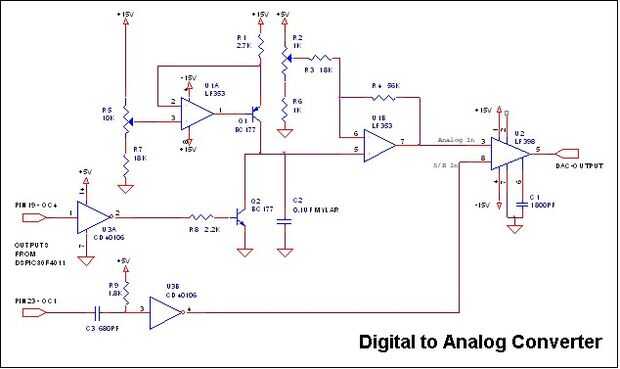

Circuitos del convertidor análogo digital

Una novela PWM basado en Digital to Analog Converter circuito ha sido realizado como parte del hardware Aj-ATE.

Simple convertidores de Digital a analógico (DAC) realizado por filtrado de pase bajo microcontrolador genera Pulse-Width-Modulated (PWM) indica una respuesta que suele ser una décima parte de la frecuencia de corte del filtro. Esta idea de diseño es una nueva implementación de un método se describe en (referencia 1) empleando una rampa de referencia cuya producción es muestreada y sostenida por el PWM señales proporcionando una tasa de rendimiento igual a la frecuencia PWM. El circuito implementa un ±10V, 10 el pedacito DAC con un rendimiento de 20 KHz.

Un Microchip DSPIC30F4011 funciona a una frecuencia de 96 MHz de reloj y las señales PWM de captura se establecen para una cuenta de 1200 corresponde a una frecuencia PWM de 20 KHz. Señal PWM OC4 con un número fijo de 1170 se utiliza como referencia para la generación de rampa y OC1 controla el DAC PWM. U1A IC junto con el transistor PNP Q1 forma una fuente de corriente de precisión de carga del condensador C2. OC4 había invertida por IC U3A interruptores en NPN transistor Q2 por un período de 30 cuentas generando una rampa nominal 0-5V en el condensador C2. La rampa es tamponada por IC U1B y amplificada, la ganancia y offset se ajustan por los potenciómetros R5 y R2. Señal PWM OC1 diferenciados por condensador C3 y el resistor R9 es invertida por IC U3B formando una señal de muestra 1uSec para el U2 de IC de muestreo y retención. U2 Pin 5, forma la salida DAC y se ajusta a - 10V, 0V y + 10V para cuentas OC1 PWM de 88, 600 y 1112 respectivamente, correspondiente a una cuenta de 10 Bit de 1024.

El recuento de 88 ayuda a evitar la región no lineal inicial de la rampa que la DAC PWM muestra buena linealidad un LSB de 20mV y una exactitud de ± 40mV. PWM-DAC adicional podría aplicarse también con salidas de PWM captura OC2 y OC3.

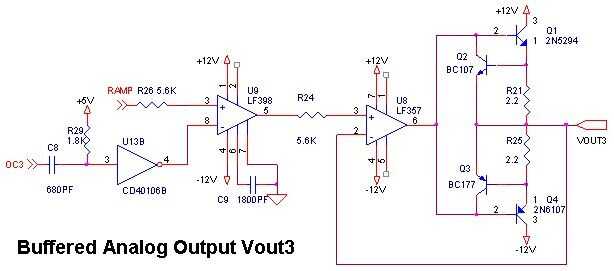

Vout3 con salida analógica

Se muestra la cadena de la señal de PWM a analógico para Vout3. OC3 es el PWM de salida que tras la diferenciación por C8-R29 e inversión por U13B forma la entrada de muestreo y retención a S/H IC LF398, U9.

El 9:50 rampa V forma la entrada de señal a un S/h. IC LF398, U9. La salida del U9 es la-buffered señal analógica correspondiente a Vout3.

Salida IC U8 está protegido por una simple etapa push-pull de clase B formada por Q1 y Q2. La combinación de U8, de Q1 y Q2 forma una etapa buffer y amplificador no invertir unidad ganancia. Los transistores Q2 y Q3 junto a R21 y R22 limitan la corriente de salida hacia ±300mA.