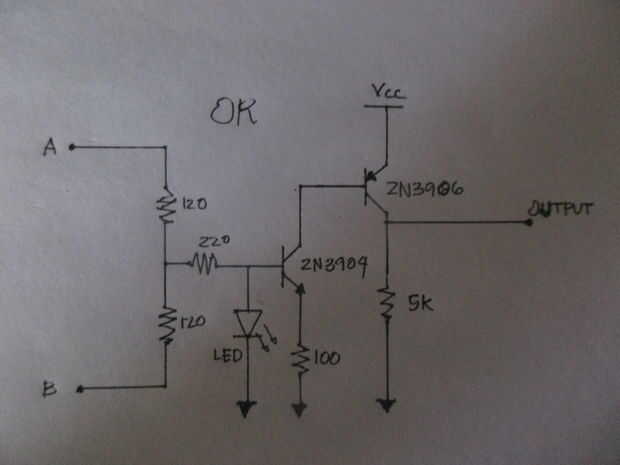

Paso 2: Diseño de circuitos

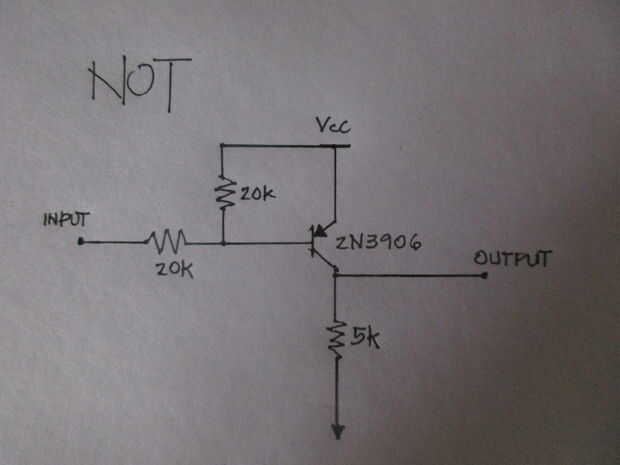

En el diseño de ambos o y no de la puerta, he usado un transistor PNP en la salida. Basado en la experiencia, un transistor PNP tiene un VCE inferior o una tensión de saturación colector-emisor mínimo cuando opera en, adivina qué... la región saturada. A veces llega 0.5V o incluso tan bajo como 0.05 mV cuando se aumenta grandemente el Vbe del transistor justo debajo de su valor máximo antes que sopla para arriba. Pero ¿por qué queremos un VCE mucho más pequeño? Para que la salida sería bastante cerca de Vcc siguiendo dichos criterios anteriores.

En el circuito esquemático, el Vbe de los transistores PNP de salida se miden para ser más 0.73V lo suficiente como para operar en la región saturada. Sin embargo, puede modificar el diseño Presione más y tener un Vbe de más de 1V. Sólo tenga cuidado de no suministrar con más de 6V puesto que si no me equivoco, 6V es el máximo permitido de Vbe para funcionar el transistor (hoja de verificación).

También debido a la configuración del PNP en la salida, cuando el transistor está en la región de corte, la salida va tan bajo como 0V debido a la resistencia de 5 K conectada a tierra una vez más, siguiendo dichos criterios.

Ahora ¿qué tal el efecto de carga? Bueno, debido a la configuración del transistor en la salida, carga del efecto sería insignificante y sin importar la carga de salida, la tensión de salida sería constante puesto que no cambia el hecho de que estamos forzando al salida transistor funcione en saturación atajo-off y es principalmente dependiente en el valor de su Vbe, no la resistencia de salida. De esta manera podemos cascada cualquier combinación de las dos puertas de la lógica sin compensación en los bornes de entrada y salidos de cada etapa/puerta.