Paso 6: Diseño de hardware interno

En este paso me he centrado en el diseño de hardware en el SoC. Zynq

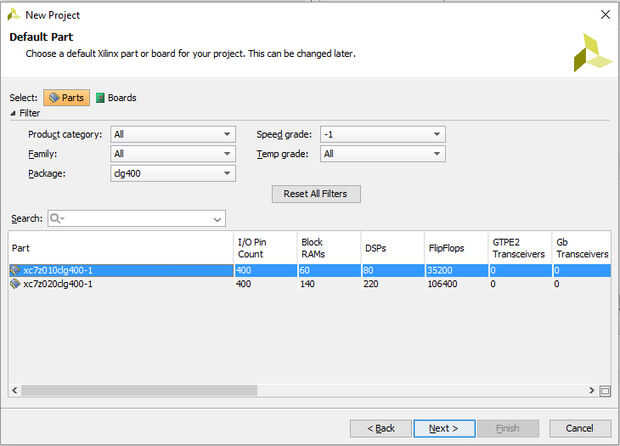

- Se crea un nuevo diseño con el hardware presente en el tablero (XC7Z010CLG400-1).

- Un sistema de procesamiento de brazo de ZYNQ se utiliza como el dispositivo principal (MicroBlaze alternativamente pueden ser utilizado en caso de FPGAs - pero esto se tratará en otro instructivo). La configuración básica se puede descargar desde el Centro de recursos

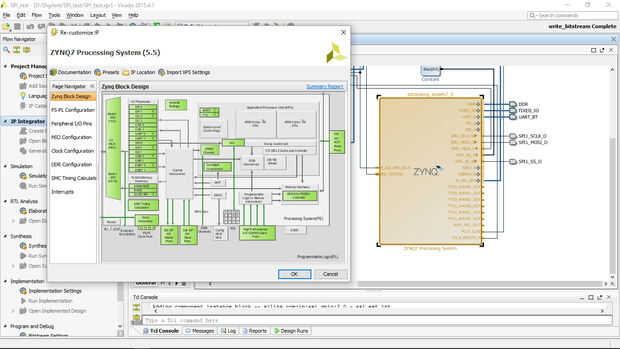

- Personalización de algunos se debe hacer a mi dispositivo: BL2 el módulo se conectará a un conector PMOD para un periférico UART se debe asignar a pernos EMIO. El ADS1299 se comunica en el protocolo SPI, por lo que el SPI es outrouted también. Un periférico I2C es necesario el EEPROM serial con dirección MAC. Tenemos que activar el temporizador y el temporizador perro guardián en la base del brazo. Por último, pero no menos el controlador de interrupción Global debe ser editado habilitando los puertos de interrupción compartidos de la tela de la interrupción de PL-PS.

- La tarjeta SD periférico debe estar habilitada y protección contra la escritura poco empatando a 0.

- Ahora los pines EMIO deben tener unos números de puerto. Esto puede hacerse mediante la adición de un archivo de restricción. Con las opciones editar conjunto de restricciones y agregar restricción podía crear el archivo XDC. El ZYBO pin deffinitions puede encontrarse en el manual de referencia.

El archivo XDC tiene la siguiente sintaxis:

La primera fila los mapas un pasador interno (como UART_txd) con un conector externo (como W14), mientras que la segunda fila establece las normas de ese pin.

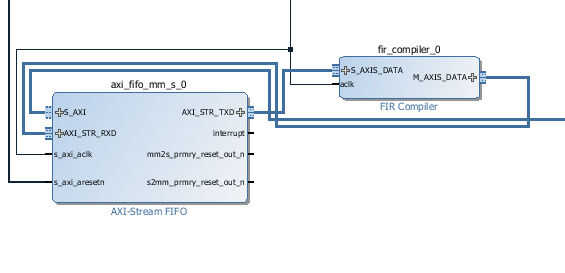

Por ahora he añadido solo un abeto compilador IP para propósitos de prueba, pero el filtro se sustituirá más adelante con IIR + abeto versiones hechas en HLS.

Para trabajar con el IP de compilador de abeto, un bloque de secuencia de AXI debe agregarse al sistema con puertos de anchura de datos coincidente o más grandes. Los coeficientes de abeto se salvaron de la herramienta de la FDA en un archivo .coe en hexadecimal, 16 bits enteros firmados.

Con esto hemos hecho un hardware listo para la prueba inicial de la base del hueso pelado que contiene el software de adquisición y la base con el sistema operativo en él. El único paso a realizar es generar un flujo de bits e importar el diseño a SDK.