Paso 3: Programación de la FPGA

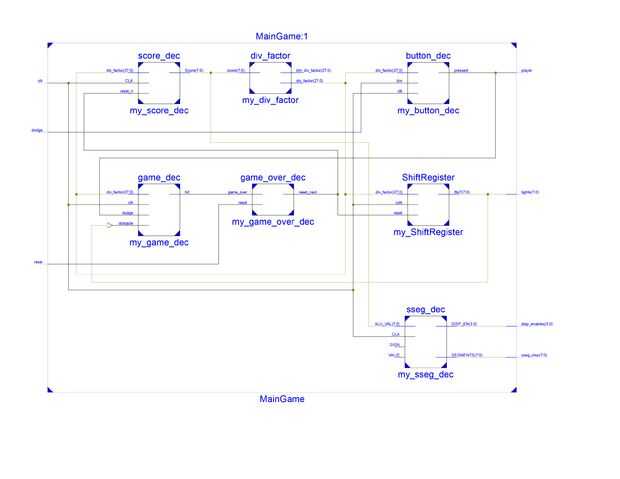

Usando la Suite de diseño Xilinix puede montar los archivos en un sistema de trabajo de módulos. Usted puede seguir estos pasos aquí para conseguirlo. Para un genio técnico como usted montar esto no debe es gran cosa, pero si necesita más explicaciones sobre los módulos, hay comentarios en los archivos vhd subido. Puede ignorar las notas debajo de cada parte en este paso si usted no necesita una explicación sobre cómo implementar el módulo porque eres un genio tal técnico.

Una cosa más antes de llegar a este

Para un más claro, o más en el diagrama de caja negra de profundidad.

-Descargar y sintetizar nuestros módulos de vhd

-Ampliar la opción de sintetizar y haga doble clic en "Vista esquema RTL"

-Haga doble clic en diagrama de caja negra para ampliarlo

Parte 1. Crear un registro de cambio para los obstáculos. Necesitará un divisor de reloj para hacer pasar obstáculos de registro ejecuta a velocidades de comprensibles.

-Inicialmente, dar el registro de desplazamiento de 8 bits a '1' para empezar los obstáculos.

-en cada rising_edge(clk) después de que

---Cambiar los bits hacia abajo pasando el (HDL 6 0) al (7 p 1) de la señal de "next" (lfsr_next) como la llamamos

---Establezca el 1 º bit de la señal de "next" en la punta del registro actual "xor" otro pedacito del registro actual

---Usted puede elegir cualquier dos bits para xor, esto sólo resultará en una orden pseudoaleatoria.

---Tiene algunas propiedades al azar, pero el patrón se repite.

Nota 1: decodificador SSEG y Clk_div son dada a nosotros por nuestro maestro. Estos módulos fueron creados por el profesor Bryan Mealy en Cal Poly Slo. El decodificador sseg toma un número de 8 bits y muestra ese número en decimal en el display de siete segmentos. El clk_div es un divisor de reloj que se extiende el período de clk. Basta con copiar, pegar en. ADVERTENCIA: El decodificador sseg puede producir advertencias de cómo el contador es inusitado. Esto es porque el contador no llega a esa alta de un número que requieren ciertos bits. Así vhdl optimiza los pedacitos y escupe una advertencia.

Prueba de que estos módulos funcionan por subir el programa y viendo los LEDs encienden. Si se realiza correctamente, el cerebro debe estar pensando que el patrón de luz que emite está en movimiento como obstáculos a la izquierda. En el caso no es así, Compruebe la configuración del tablero, los módulos y su propio cerebro.

Parte 2. Crear el decodificador cuenta. El módulo de salidas una puntuación basada en el tiempo, esencialmente es un contador. Ningún juego está completo sin una manera fría, objetiva de distinguir lo malos es en comparación con otros. Asegúrese de crear un módulo similar a sseg_dec.vhd para que usted y sus compañeros de jurado pueden ver el resultado en el display de siete segmentos con facilidad.

-En el flanco ascendente de la clk después de ser puesto a través de la clk_div, incrementar la puntuación

Prueba si funciona por que lo simula. Asegúrese de que el incremento de números correctamente. Entonces usted puede probar más enviando la salida del decodificador de puntuación a la sseg_dec para determinar que funciona visualmente. La puntuación debe aumentar por uno para cada flanco ascendente de reloj.

Nota 2: Cuando simulando el decodificador de la puntuación, la ventana de simulación es dentro de unos pocos nanosegundos, por lo tanto reduce su factor de reloj a 1 para los resultados apropiados. De lo contrario nada parece estar sucediendo.

Parte 3. Combinar el Shift Register y el decodificador cuenta con un módulo principal. Asegúrese de que el divisor de reloj como el reloj de registro de desplazamiento y la puntuación. El resultado final debe tener un puntaje incrementos en cada turno de los obstáculos.

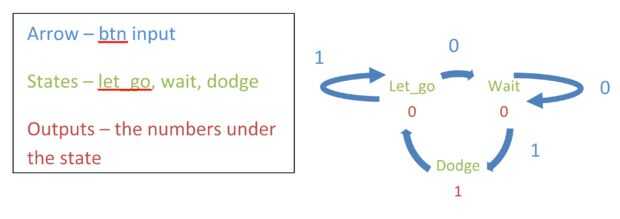

Parte 4. Crear un módulo para el decodificador botón. Toma en la entrada de un botón y determina si el reproductor está en esquivar estado o no. Esto es necesario para evitar que los jugadores de mantener pulsado el botón de esquivar y esquivar todos los obstáculos que se aproximan.

-Este módulo puede ser representado usando una máquina de estados finitos, representada en el diagrama adjunto estados finitos

-Por defecto es esperar estado

-Si usted no presiona el botón el estado permanece en modo de espera

-Si lo hacen, entonces va a modo de esquivar y salidas del regate para un tiempo

---Esto es determinado por un clk que cuenta cierto número en el borde de levantamiento (hasta usted)

-Después de terminar el modo de aclarado, automáticamente pasa a estado de let_go y no volver a esperar el estado hasta que el jugador deja ir el botón.

Parte 5. Crear un módulo para comprobar si el jugador es golpeado por el bloque y que el juego es terminado.

-El juego es sobre si es el obstáculo en el final y el jugador no está en modo de aclarado.

-Si el juego termina, usted puede restablecer el registro de desplazamiento y el score_decoder, lo que hicimos

---O se puede esperar a un usuario a reiniciar el juego

Esto fue probado con un archivo de simulación. Ponemos las entradas a diferentes combinaciones y corrección visual confirmado.

Parte 6. Esto poner todos juntos en le modulo principal y ejecutar el juego con el archivo de restricciones.

-Las asignaciones de las clavijas de más pueden encontrarse en el tablero.

-Para los cables de LED que se van a conectar, tendrás que buscar en la Web de la Junta. Si utiliza un tablero de SDMONEXYS 3, puede utilizar nuestro archivo de restricciones e implementación que comenta qué pernos están en el tablero.

-Prueba con simulación así. Es fácil ver lo que sucede con un archivo simulado puesto que usted puede mirar en las salidas de los módulos individuales también.

Nota 3: Usted conseguirá las mismas advertencias como Nota 1 con algunos otros módulos por la misma razón.

Parte 7. Opcional. (Obligatorio si todas las partes antes de esto fueron una brisa para usted) Modificar todo con un divisor de reloj y el decodificador de botón en la cuenta (no hacer esto para el decodificador sseg). De esta forma que la puntuación aumenta puede pasar a una cuenta diferente y acelerar el juego para aumentar la dificultad.

Nota 4: Si haces esto, usted puede obtener algunas advertencias adicionales, indicando que ha creado un seguro. También las simulaciones se realizaron antes de esto, así que tendrás que añadir las asignaciones si desea simular después de la adición.

Nota 5: Usted puede obtener una advertencia de que algunas cosas se se obtienen con una clavija de combinatoria. Esto está muy bien, no afecta el juego.

Parte 8. Cargar el archivo de bits en el FPGA. Porque a pesar de todo este trabajo, la FPGA todavía no hace nada. Para hacer esta descarga e instalar un programa llamado a Adept.

Puedes encontrarla aquí http://www.digilentinc.com/Products/Detail.cfm?Nav...

Una vez instalado conectar el cable micro del USB a la FPGA y seleccione el archivo de bits. Luego presione program. Si llegue a esta parte sin saltarse los pasos un pequeño juego que llamamos nuestro proyecto debe estar sentado frente a ti.