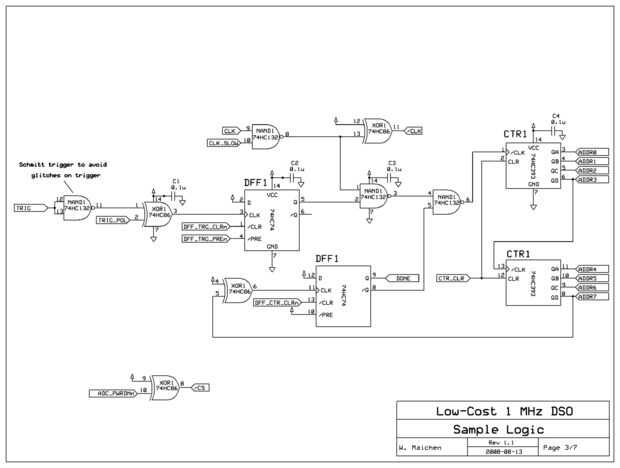

Paso 7: Descripción - muestra lógica del circuito

Originalmente diseñé el alcance usando un CPLD Xilinx (dispositivo lógico programable), pero en fin

decidió emplear virutas de Lógica CMOS estándar (serie 74HCxx) en su lugar - un CPLD tiene nuevo hardware programación especial y software y me imaginé que pondría probablemente de todo el mundo excepto algunos expertos. También golpeó un poco el costo del componente. Esto me obligó a reducir realmente la lógica de contenido a un mínimo absoluto, por lo que hay por ejemplo ninguna opción de pre-disparador (es decir, una posibilidad para capturar la señal antes de la activación). Tal vez voy a hacer tal alcance en el futuro.

El microcontrolador proporciona una señal de reloj (producida en el fondo a través de su salida PWM)

que es cerrada (bloqueado) hasta que un impulso de disparo llega a través del flip-flop DFF1. La XOR delante de

DFF1 actúa como un inversor programable para seleccionar activación en el borde de levantamiento o caída. Delante de él es una puerta de lógica Schmitt-trigger que añade cierta histéresis para minimizar la posibilidad de falsas alarmas debido a ruido.

La señal de reloj lleva un contador binario de 8 bits (CTR1) que incrementa la dirección de los datos

almacenamiento en el SRAM (ver página siguiente). Cuando el contador se envuelve (es decir, después de alcanzar su

máximo y el bit más significativo se vuelve de 1 a 0) esto desencadena otro flip-flop (el

la segunda mitad de DFF1) que a su vez las puertas de la señal de reloj. La otra salida (Q) del flip-flop

produce la señal de "Listo" que indica al microcontrolador que ha terminado la adquisición de datos y los datos ahora pueden ser leídos de la memoria de muestra y transferir al PC.

Para esta lectura, el microcontrolador permite volver a la senda del reloj y alternativamente impulsos de la señal de reloj y lee un adiós de los datos de la muestra, que transfiere a la PC a través de la conexión en serie.