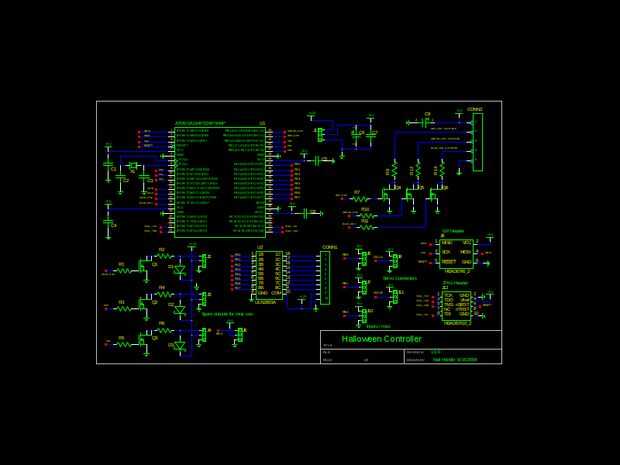

Paso 1: El esquema del diseño del controlador

El controlador se basa en un ATMega324P en paquete TQFP 44 pin. El esquema fue dibujado en herramienta de gschem de gEDA. Mirando el esquema que se adjunta en ambos PNG y en formato de gEDA/gschem.

Un ánodo común de RGB que LED se conecta en CONN2, este es un modelo de 3W de Everlight que encontré superávit. Cada segmento de este LED puede manejar 3W por lo que fue necesaria para conducir los cátodos con transistores de potencia A5 y Q4 y Q6. Este AVR particular fue escogido pues trae 3 canales de PWM de los temporizadores internos a los pines. Esto permite el control independiente de brillo de los canales de color R, G y B.

Una cabecera de ISP (J9) y JTAG (J12) se sacó de programación y depuración. Sólo la cabecera del ISP es necesaria, pero yo quería experimentar con JTAG, así.

La CPU (U1) es registrada por un cristal de 20MHz, X1.

La Junta funciona con 5V, con la opción de un paso de 12V en un momento posterior.

Otras funciones que no son necesarios para este propósito incluyen U2 un ULN2803A alta potencia buffer para la conducción de otra carga desde Puerto A de la CPU, así como 3 canales que pueden conducir el Relais a 12 V en J2, J3 y J4. Las salidas de temporizador que se utilizan no son puestas hacia fuera en J8 y J11 eventualmente controlar servomotores. IO de propósito general (GPIO) se proporciona en J5, J7 y J10.