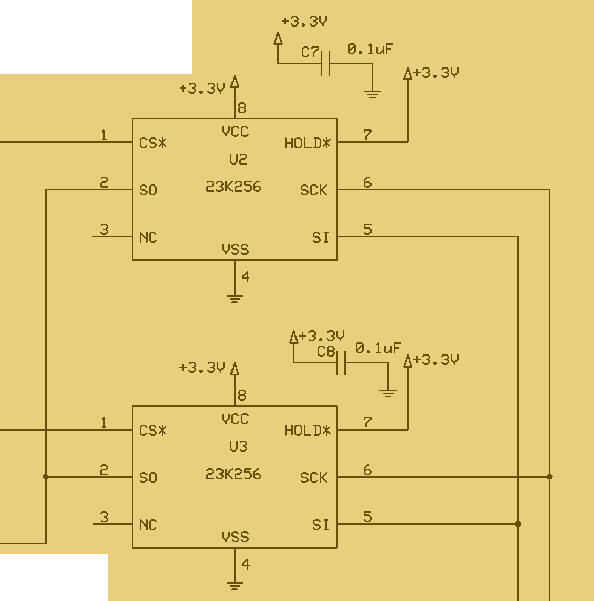

Paso 5: SPI RAM

La RAM utilizada aquí se comunica con el microprocesador mediante la interfaz SPI. Son los condensadores C7 y C8

Condensadores para las dos fichas de derivación.

Este diseño guarda las muestras de forma de onda como valores de 8 bits. Como tal, no ofrece gran

fidelidad de audio, pero es mejor que la calidad de radio AM. Este circuito fue diseñado para utilizar 23 de Microchips K 256

Chips de memoria RAM, que son de 32 k bytes de tamaño. (32k por 8). Consulte la hoja de datos para la parte para más detalles

Acerca de su funcionamiento.

La memoria RAM se utiliza como un gran buffer circular. La cantidad máxima de retardo posible depende del tamaño

de la memoria intermedia y la tasa a la cual se muestrea la señal de entrada. El programa lazos constantemente, almacenar

nuevas muestras en la RAM con cada lazo. Cuando el número de muestras supera el tamaño de la RAM, se

envuelve más y sobrescribe las muestras más antiguas.

El sistema puede usar uno o dos chips de RAM, dependiendo de cuánta capacidad es necesaria. Si dos

Carneros se utilizan, a continuación, tire el resistor R13 debe ser utilizado en el chip seleccione línea. Esta línea se muestrea

por el microprocesador al arrancar, y si se tira alto, el programa estará configurado para dos carneros.

El programa ajustará automáticamente la forma de que la dirección se maneja, por lo que son los dos carneros

tratados en el software como un gran buffer. La entrada de CS de la segunda memoria RAM debe ser tirado alta

a través de un resistor no conectado directamente a VDD. Si está conectado directamente a VDD, se corta VDD a

tierra cuando se tira el chip seleccionar línea baja y el procesador es probable que dañarse. Cuando sólo uno

RAM se utiliza, la línea se tirará baja, también a través de una resistencia en lugar de directamente a tierra.

Como se mencionó anteriormente, el retardo máximo depende el tamaño del búfer y la frecuencia de muestreo. Cada

muestra es un byte. La cantidad máxima de audio, en segundos, que pueden ser almacenados luego viene dado por:

Max Delay (en segundos) = tamaño (en bytes) del búfer / frecuencia de muestreo (en muestras por segundo)

Así que, si uno utiliza chip de byte RAM de 32 k y la frecuencia de muestreo es 11025 muestras por segundo, la máxima

retardo que puede ser producido es:

Max Delay = 32768 / 11025 = 2,972 segundos

Si la frecuencia de muestreo es de 8000 muestras por segundo el retraso máximo es:

Max Delay = 32768 / 8000 = 4,096 segundos

Si se usan dos chips de memoria RAM, los tiempos de retardo máximo sería 5,944 segundos y segundos 8,192, respectivamente

para el 11025 y 8000 muestras por segundo tarifas.