Paso 2: Programación de Hardware

Este paso es una introducción a la programación de hardware. Si ya hiciste alguna programación de verilog puede omitir este paso.

¿Cómo se programan los FPGAs?

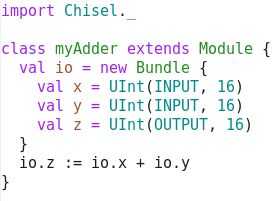

Programar una FPGA es diferente a otros estilos de programación. En lugar de dar las instrucciones a ejecutar en orden, se describe el diseño del hardware. Describir en un solo bloque sería muy desordenado y difícil de leer sin embargo. En cambio, similar a las funciones en otros idiomas el hardware se divide en módulos. Estos módulos están conectados juntos para hacer diseños más complicados. Cada uno de estos módulos de entrada y de salida. Al conectar estos módulos juntos similar a llamar a las funciones podemos crear complicados diseños legibles. La imagen muestra un ejemplo de un módulo en cincel que suma dos números. La línea superior de las importaciones cincel. Usted necesitará hacer esto en todos los archivos de cincel. A continuación declaramos un módulo de serpiente llamado myAdder. Este agregado tiene dos entradas x e y para calcular el resultado z = x + y. UInt es abreviatura de 'entero sin signo' declarado como entrada o salida con 16 bits. Cuenta cómo es ": =" no "=". Esto es muy importante pero será explicado más adelante. El siguiente paso será demostrar cómo conectar módulos en cincel.

Algunos conceptos básicos conceptos de Hardware

Esta sección describirá algunos de los conceptos en el diseño de hardware.

El reloj

El reloj es esencial para entender el diseño de hardware. Es un reloj que sincroniza su diseño para que todo funciona a la misma velocidad. Hardware se divide generalmente en dos categorías: lógica combinacional y secuencial. Lógica combinacional como a = b + c ignora el reloj. Lógica secuencial utiliza el reloj para determinar cuándo leer en nuevos datos en un elemento de memoria. Un registro o Reg en cincel es un ejemplo de un elemento de lógica secuencial. Cada vez que el reloj de 'relojes' el valor de la entrada del registro es recordado para más adelante. En cincel está implícito el reloj. Esto significa que no necesitará preocuparse por conectar.

Ruta crítica

La ruta crítica en su diseño determina qué tan rápido puede correr el reloj. Generalmente el más rápido, mejor. La ruta crítica es la ruta más lenta combinatoria entre cualquier dos registros. Considerar en términos de una carrera entre el reloj y el camino más lento. El reloj tiene que ser lento lo suficiente para que los datos pueden correr a través de la ruta crítica al registro donde se almacenarán. Su diseño puede ser correcto pero lento si no piensas en él.