Paso 2: Componentes del circuito

Diseño de los componentes:

Para poder implementar un sintetizador en el tablero de SDMONexys 2 FPGA, varios componentes deben ser diseñados. A partir de las salidas, los módulos deberán manejar encender LED y salida de funciones de onda cuadradas al altavoz. También se necesitarán módulos debounce entradas de botón y generar un pulso de reloj solo una pulsación. Por último, módulos como contadores, flip-flop, multiplexores se necesitarán para manejar la lógica restantes de almacenar notas y reproducir secuencias correctamente.

La lista siguiente contiene una breve descripción de lo que hace cada componente de este proyecto, cómo cada componente está siendo utilizado y cómo implementar estos componentes en VHDL:

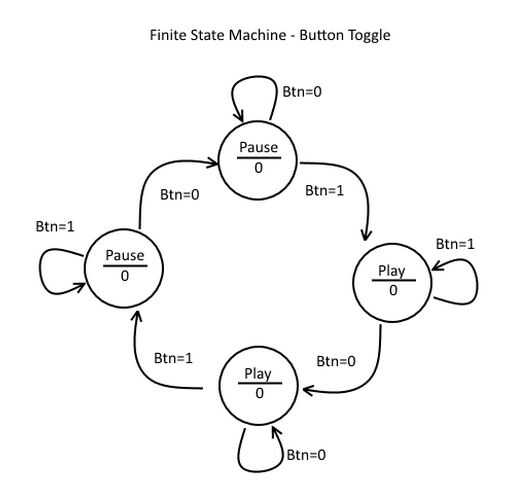

Botón de alternar: En el caso del botón de play/pause, queremos alternar entre dos Estados exactamente una vez cuando se presiona el botón. Para ello, utilizamos una máquina de estados finitos (FSM). Así, después de la transición entre Estados una vez que el circuito de alternar botón no permitirá que otra transición de estado a ocurrir hasta que el botón ha sido liberado y luego vuelva a presionar. Arriba se muestra un diagrama que representa este FSM.

La máquina de estado finito contiene dos Estados para cada salida posible. Comenzando en la parte superior del diagrama del FSM, el circuito es en el estado de pausa. Tan pronto como se pulsa el botón, el circuito irá al estado de juego. Permanecerá en este primer estado del juego hasta que se suelta el botón. Ahora, el circuito es todavía en el estado de juego, pero está listo para el botón al ser presionado otra vez a la transición al estado de pausa. Del mismo modo, el circuito una vez más se espera el botón para ser lanzado antes de que sea listo para cambiar el estado del juego.

Divisor del reloj: El circuito divisor de reloj simplemente convierte la frecuencia de 50 MHz de 2 SDMONexys a una frecuencia mucho menor. Esto se utiliza para establecer el valor de BPM (beats por minuto) del sintetizador. En este proyecto estamos utilizando un módulo VHDL escrito por Bryan Mealy de California Polytechnic State University, San Luis Obispo.

Contra: Un contador de salidas simplemente un número binario. Cuando su entrada es alta, aumentará este número 1 en el flanco ascendente de reloj. Los contadores utilizados en este circuito utiliza T flip-flops para almacenar un número de 3 bits. Cada flip-flop representa un bit almacenado. El flip-flop que representa el bit menos significativo alternará cada vez que el contador va a incrementar. Otros flip-flop cambiará cuando todos bits por debajo de ellos son iguales a uno. Este comportamiento también lo hará así cuando el contador alcanza el más alto 111(binary) número, posible, volverá a cero cuando se incrementa a continuación.

En este proyecto, se utiliza un contador de ritmo actual para que el orador sabe que tono para jugar, así que puede activar el LED correcto. Un contador también se utiliza para mantener el tono actual que puede ser introducido por el usuario.

Debouncer: Los botones en el tablero de SDMONexys 2 FPGA no son perfectos. Idealmente, cuando presiona los contactos toquen exactamente una vez y permanecer juntos hasta que se suelta el botón. En realidad, los contactos tienen una tendencia a "rebotar" en múltiples ocasiones, que cuando se presiona el botón los contactos vendrán dentro y fuera de contacto varias veces antes de pegar. En cuanto a nuestro sintetizador, esto podría conducir a un botón de play/pause que pasa entre los dos Estados varias veces cuando se presiona el botón y no se garantiza que la tierra en la correcta. Para contrarrestar esto, un circuito debounce esperar cierto tiempo para la entrada "establecerse".

En este proyecto hemos utilizado un módulo VHDL escrito por Scott Larson de Digi-key, publicado originalmente en el wiki EE de Digi-key.

Generador de pulso: Los contadores utilizados en este proyecto avanzará junto con una cierta frecuencia de reloj como se habilitan. Para algunas funciones, tales como incrementar la frecuencia cuando se presiona el botón para cambiar el tono actual, podríamos querer incrementar un contador solamente una vez con cada pulsación. Esto requiere tomar una entrada y convertirla en un pulso con una duración de ciclo de exactamente un reloj. El circuito del generador de pulso hará esto. Cuando su entrada va a alto, su salida va alta para ciclo de exactamente un reloj. Esto se logra mediante un seguimiento de la entrada de corriente para un determinado borde de levantamiento del reloj, así como la entrada anterior para el último flanco ascendente de reloj. En el caso donde la entrada de la corriente es alta y la entrada anterior es baja, la salida es alta. De lo contrario, la salida es baja. En VHDL, esto se logra mediante un modelo de comportamiento. Un bloque de proceso comprueba los valores de los incr del valor de entrada y la entrada anterior incr_prev en el flanco ascendente del reloj. Si incr es uno y incr_prev es cero, la salida q se encuentra a uno. De lo contrario, q se ponga a cero. Finalmente, incr_prev obtiene el valor de incr.

sseg_dec: Este circuito toma un binario con 8 bits de entrada y muestra como un número decimal en el display de siete segmentos Nexys2. En este proyecto, estamos utilizando un módulo VHDL escrito por Bryan Mealy de California Polytechnic State University, San Luis Obispo.

Cuadrado generador de ondas: Este componente genera una onda cuadrada basada en una entrada de 3 bits. Lo hace dividiendo la señal de entrada de reloj por un número específico para lograr la frecuencia deseada. La salida se enciende y apaga según esta frecuencia. Hay siete frecuencias predeterminadas, basadas en la escala pentatónica, que representa las notas desde A4 hasta C6. Las frecuencias de estos tonos van de 440 Hz a Hz 1046,5. Si la entrada es 000(binary), no se juega onda cuadrada.