Paso 8: Vídeo rutina

- Interfaz periférico serial (SPI) - dsPIC33F

- Acceso a memoria directo (DMA) (parte III) - dsPIC33F

- Salida compara - dsPIC33F

Debemos generar la señal de vídeo se compone de tres partes: la señal de sincronismo horizontal (TTL 0v - 5v), sincronización Vertical (TTL 0v - 5v) y las señales de tres colores (rojo verde azul, analógica 0v - 0.7v). La imagen es elegida para ser monocromático, las tres líneas de color se unen como sólo pueden asumir dos niveles. Las capturas de pantalla la imagen recibida pasada se guarda internamente y mostrar en la pantalla del monitor, cada una de estas imágenes se llama un marco. Nuestra misión es crear estos marcos en la frecuencia que el monitor consuma. Las imágenes están 'pintadas' en la pantalla como se muestra en la primera imagen, línea por línea, de izquierda a derecha, solo como lectura.

Cada nuevo marco allí está marcado por una señal, llamada el pulso de sincronización vertical. Otra señal llamada la sincronización horizontal, generan pulsos continuos. El pulso horizontal nunca se detiene, pero los impulsos de la primeros y la últimos en un marco son desechados por el receptor. Los 800 pulsos horizontales en medio de un marco son las que indican las líneas que se muestra en la pantalla. En algún momento entre los bordes de la señal de horizontal se pone el color de cada píxel en esa línea se pone en la línea RGB (negro = 0v, 0.7v = blanco). La elección de un reloj de 40 MHz facilita la generación de la señal de vídeo porque la frecuencia de cada uno de estos píxeles es de 40MHz para una resolución de 800 x 600. Cada píxel se serializa desde el búfer de vídeo por el módulo SPI, cada bit de la solución de video se estira para llenar cuatro pixeles.

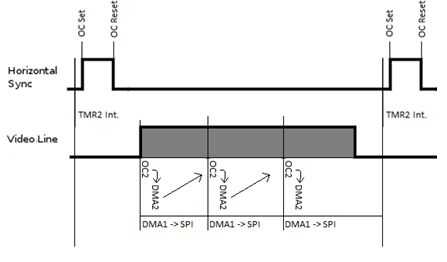

El módulo de video es controlado por el temporizador 2 programado para desbordar en exactamente la frecuencia de la señal de sincronismo horizontal. Para generar esta señal la salida comparar módulo se utiliza para activar un pin de la computadora automáticamente. La interrupción de temporizador 2 se utiliza para decidir si este es el comienzo de un nuevo marco, controlar la sincronización de la señal vertical. La interrupción que controla la señal de sincronización Vertical toma algún tiempo para que funcione y esto puede resultar en problemas en la sincronización de marco, para corregir esto la horizontal señal sync también tiene este retraso añadido a él dejando las dos señales sincronizadas.

Con estas dos señales sincronizadas correctamente ya tenemos un marco sincronizado. Nuevo tenemos que pintar la imagen. El módulo SPI se utiliza para serializar una palabra (16 bits) poco a poco a través de un pin del micro. Cargar el módulo directamente llevaría casi todo el tiempo de procesador y no sería viable. Un canal DMA se utiliza para transferir un búfer pequeño 'línea' para cada línea a ser serializado (leer 'pulso de sincronismo horizontal'). El buffer debe ser cargado de partida del búfer vídeo antes de cada línea en la rutina de interrupción de TMR2, que sucede justo antes de una nueva línea. Y antes de cada transferencia de DMA debe activarse en el momento adecuado para empezar a serializar los bits.

Cuando utilice el módulo SPI propio IRQ a la DMA allí es un problema, después la IRQ y antes DMA transferencia hay una demora, lo que genera un pixel de ancho cada 16 píxeles. Una forma para resolver este problema es generar un IRQ tiempo para solicitar el DMA para cargar el SPI.

Para generar esta IRQ programada otro módulo DMA y un módulo OC están conectados juntos. El DMA cambiar el tiempo de interrupción de la salida compara transfiriendo un búfer a él. Cuando el OC tiene una interrupción desencadena la DMA, recibiendo un nuevo tiempo para interrumpir y continuar el bucle.

Que para la transmisión de una línea de video (200 píxeles), el procesador sólo tiene que cargar la línea buffer antes de cada línea. La línea del almacenador intermediario podría ser eliminada si este micro DMA podría cubrir toda el RAM (se limita a sólo 2K) leyendo directamente en el búfer de vídeo. La segunda imagen es tratar de explicar esto.