Paso 13: Configuración de apagado/UVLO

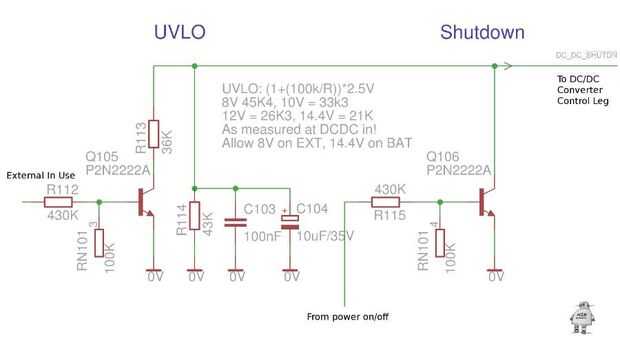

Con el convertidor DC-DC "habilitar" liberada por encima de la pierna, ahora es posible electrónicamente activar y desactivar la energía deteniendo el convertidor buck--esto es impulsado desde el chip de cierre cierre de energía través de Q106.

El bajo voltaje de bloqueo (UVLO) detiene el convertidor DC-DC de funcionamiento si la batería está agotada, o el voltaje de entrada externo es insuficiente. Hay dos diferentes niveles seleccionados. Uno para la energía de la batería y otro para alimentación externa. Batería: 14.4V (0.9V celular), en energía externa: 8V

La hoja de datos MP2307 muestra los cálculos de UVLO, que se repiten en el esquema.

- R114 se utiliza en alimentación externa: 43K = (8.1V mínima en la entrada).

- R114 + R113 en paralelo a través Q105 cuando en batería: 43K en paralelo con 36K da (14.4v en batería)

Nota: Entrada de UVLO medido en el convertidor DC_DC no es la batería la tensión de entrada de tensión externa real debido a las pérdidas en FETs/diodos así debe ajustarse para 14.4V en la batería y 8V en la DC entrada.

Ajuste/verificación, estos se hace mejor con una fuente de alimentación variable externa, en lugar de la batería/actual PSU.

C103/C104 prevenir glitching pasando del exterior al poder interno y, por este punto para hacer más lento su reacción ante el cambio de "slugging". De lo contrario el convertidor abandona momentáneamente.