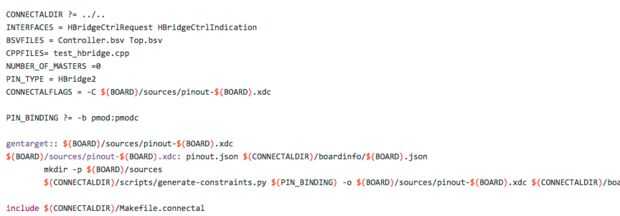

Paso 10: Makefile

CONNECTALDIR: Si se compila en su propia máquina, utilice esta variable para que apunte a la ubicación del árbol de fuentes de Connectal que se construyen contra. Si está utilizando el servidor de compilación, deje este sin cambios puesto que se define como una variable de entorno por Buildbot.

INTERFACES: Esta lista contiene los nombres de las interfaces de bsv que pueden utilizarse como portales. SW enviar comandos al controlador de HW a través de la interfaz 'HBridgeCtrlRequest', y HW reportará eventos asincrónicos a SW a través de la interfaz 'HBridgeCtrlIndication'.

BSVFILES: Esto muestra los archivos de bsv específicos de este proyecto. Controller.BSV implementa la lógica de control y Top.bsv une todas las piezas.

CPPFILES: Esto muestra los archivos cpp específicos de este proyecto. Los componentes de SW del controlador se ejecutan en un solo archivo llamado test_hbridge.cpp.

NUMBER_OF_MASTERS: Si el hardware de accede directamente a memoria del host, este conjunto refleja el número de interfaces de bus mastering que exporta.

PIN_TYPE: El componente HW de un proyecto de Connectal predeterminado interactúa con el mundo exterior a través del bus de sistema exclusivo (AXI o PCIe). Si su diseño interactúa con otros periféricos de hardware, necesita especificar una interfaz BSV suplementaria a través del cual llevará a cabo esta interacción. En este proyecto, hemos definido una interfaz BSV llamada HBridge2 a través del cual la lógica de la FPGA puede configurar los registros de control de los dos dispositivos hbridge.

CONNECTALFLAGS, PIN_BINDING, gentarget: estas tres variables de archivo make se utilizan para conectar los cables suplementarios a los pines del dispositivo FPGA (que a su vez conectan con los cables del PMod en el zedboard). Les hablaremos más extensamente al examinar cómo especificar el pinout para el proyecto.