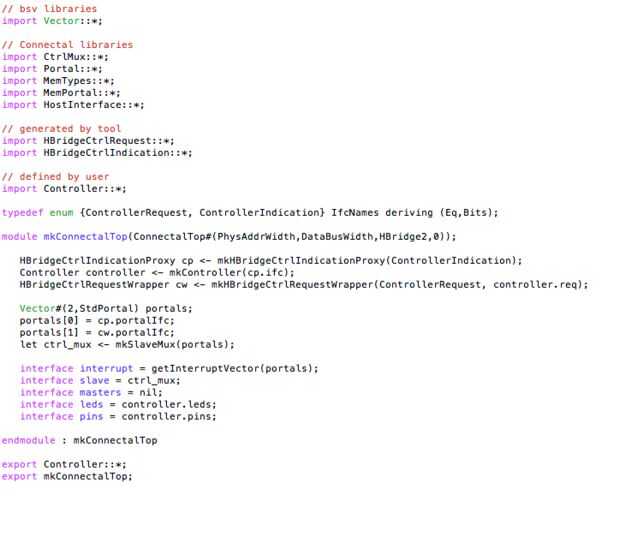

Paso 12: Top.bsv

Top.BSV crea una instancia de todo el estado interno y define las interfaces que el marco de Connectal conecta a los pines físicos del dispositivo FPGA.

En nuestro diseño, la interfaz de HBridgeCtrlIndication es implementada en SW e invoca de HW. Como resultado, nos instanciar el mkHBridgeCtrlIndicationProxy proxy generado. Este módulo cuenta con una interfaz sub 'ifc' de tipo 'HbridgeCtrlIndication' que se pasa a la mkController módulo invocarse directamente de su lógica interna. Porque HBridgeCtrlRequest es implementado en HW y desde SW, debemos envolver usando el módulo generado mKHBridgeCtrlRequestWrapper para conectar al bus. La envoltura y el proxy están conectadas al sistema de autobús de primera muxing les con 'mkSlaveMux' y la resultante única interfaz de conexión a la interfaz 'esclavo'.

El esclavo de bus y maestros, así como los leds y las interrupciones han sido asignados dedicado de la interfaces. Marco Connectal conecta automáticamente a los pines correctos dependiendo el objetivo de construir especificado. Falta definir estas interfaces no resultará en un error de compilación, pero va a resultar en anomalías de tiempo de ejecución. Por ejemplo, si el SW se basa en el sistema llamado 'encuesta' de un mensaje pendiente de HW, falta definir la interfaz de interrupción hará que el diseño colgar. Si no define la interfaz de esclavo, los proxies SW reportará una falla cuando intentan localizar la asignación correcta de registro durante el inicio.

Por último, el paquete/archivo que define la interfaz de pernos adicionales deben exportarse explícitamente que puede ser utilizado por la parte superior de la plataforma-específicas (mkZynqTop, mkBsimTop, etc.). La parte específica de la plataforma superior es seleccionada por la cadena de herramientas según el objetivo de construir. Estos archivos se encuentran en $CONNECTALDIR/bsv.