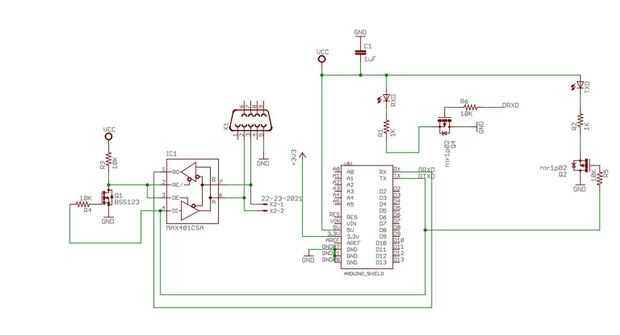

Paso 1: Análisis de circuito

Las respuestas de escudo en un chip de MAX481CSA y cambio de nivel TTL a nivel 485. Como se muestra en el esquema, las señales de activación para el receptor y el transmisor están cansadas juntos y controladas por el dren del transistor MOS Q1. El desagüe de Q1 a su vez es controlado por la señal de datos (TX). Cuando los datos transmitidos están "1", el RE / DE señal será "0" y el chip es en el Estado receptor, y el chip no impulsará A, líneas de datos diferencial de B. Si no hay ningún circuito externo hacia abajo, los datos mostrados en la línea de datos será inciertos. Esto también es una causa del error. Pero no es la causa del problema al comunicar a alta velocidad. En la siguiente sección, vamos a analizar la secuencia de sincronización, y podemos ver claramente la cuestión.