Paso 15: Implementar circuito 1 en Verilog HDL

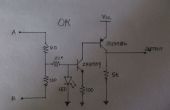

Construir y aplicar la ecuación lógica para circuito 1 según la tabla de verdad. Le construimos la ecuación lógica en forma de compensación para la demostración. En el circuito 1, tenemos dos filas (segunda fila y tercera fila) que muestra un "1" en la salida. Así que tenemos una puerta OR con dos entradas que generan la salida y dos puertas y de 2 entradas que proporcionan la entrada para la puerta OR. En la segunda fila, entrada SW0 muestra un "1" y SW1 entrada muestra un "0". Así SW0 está conectado a la entrada de la puerta y primera y SW1 se invierte antes de conectar a la segunda entrada de la puerta y, como se muestra en el primer término del producto en la ecuación. En la tercera fila, entrada SW0 muestra un "0" y SW1 entrada muestra un "1". Así SW0 se invierte antes de conectar a la entrada de la segunda puerta y y SW1 está conectado directamente a la segunda entrada de la puerta y, como se muestra en el segundo término del producto en la ecuación. La salida LD0 es la suma de estos términos de dos producto.

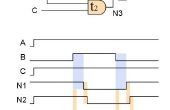

En Verilog HDL, este circuito se implementa como arriba.