Paso 3: Implementar un multiplexor de

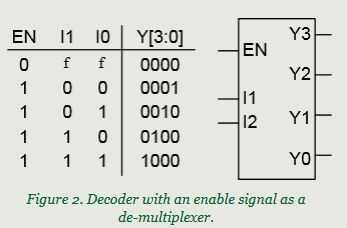

Un multiplexor se puede construirse usando un decodificador binario con una señal de enable. La definición funcional de un decodificador binario con una señal de activación se muestra en Figura 2 arriba.

En el mismo proyecto, cree un nuevo módulo de Verilog llamado demux, con 3 entradas (at, I0, I1) y cuatro salidas (Y0, Y1, Y2, Y3).

(demux) 1 módulo

2 en I0, I1, Y0, Y1, Y2, Y3

3);

4

5 entrada En, I0, I1;

reg 6 salida Y0, Y1, Y2, Y3;

7

8 / / la descripción de la conducta y

9 / / usando las sentencias if-else o caso

10

endmodule 11

El código de la funcionalidad de lo mux su comportamiento, como ya comentamos en el anterior proyecto.

Crear un banco de prueba para simular el multiplexor de y asegúrese de que está funcionando adecuadamente.