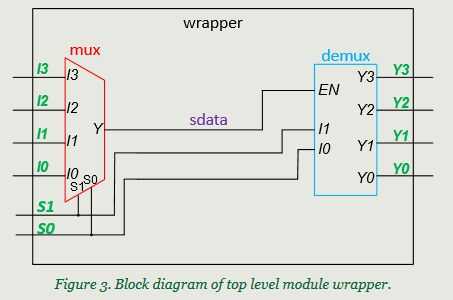

Paso 4: Crear un contenedor como el módulo de nivel superior

En este paso vamos a crear el módulo de nivel superior, en el cual un mux un mux de ser instanciado y conectados correctamente para formar un tiempo simple sistema de comunicación de la multiplexación. El diagrama del sistema se muestra en la figura 3 de arriba.

En el diagrama de bloques, los puertos de entrada/salida de la envoltura del módulo está en verde; los puertos de entrada/salida del módulo mux y demux se muestra en cursiva negra; y el cable interno del módulo de envoltura en púrpura.

En el proyecto, crear un nuevo archivo de módulo de Verilog llamado wrapper con entradas de 4 datos (I3, I2, I1, I0), 2 seleccionar entradas (S1, S0) y cuatro salidas (Y3, Y2, Y1, Y0).

(envoltura) 1 módulo

2 I0, I1, I2, I3, S0, S1, Y0, Y1, Y2, Y3

3);

4

5 la entrada I3, I2, I1, I0, S1, S0;

6 la salida Y0, Y1, Y2, Y3;

7

8 / / Descripción estructural del contenedor

9

endmodule 10

Declarar sdata alambre interno después de la declaración de entrada y salida.

1 alambre sdata;

Crear una instancia de la de-mux (llamado output_demux) y conectar los cables en la envoltura de los puertos de la entrada-salida del de-mux.

1 (demux) output_demux

2. En(sdata),

3. I1(S1),

4. I0(S0),

5. Y0(Y0),

6. Y1(Y1),

7. Y2(Y2),

8. Y3(Y3)

9);

Poner todo junto. El nivel superior módulo Verilog será como sigue:

(envoltura) 1 módulo

2 I0, I1, I2, I3, S0, S1, Y0, Y1, Y2, Y3

3);

4

5 la entrada I3, I2, I1, I0, S1, S0;

6 la salida Y0, Y1, Y2, Y3;

7

8 / / Descripción estructural del contenedor

9 alambre sdata;

10

(input_mux) 11 mux

12. I3(I3),

13. I2(I2),

14. I1(I1),

15. I0(I0),

16. S1(S1),

17. S0(S0),

18. Y(sdata)

19);

20

(output_demux) 21 demux

22. En(sdata),

23. I1(S1),

24. I0(S0),

25. Y0(Y0),

26. Y1(Y1),

27. Y2(Y2),

28. Y3(Y3)

29);

30

endmodule 31

Crear un archivo XDC como sigue:

-I3 a SW3; I2 a SW2, I1 a SW1, I0 a SW0

-Y3 a LED3; Y2 a LED2, Y1 a LED1, Y0 a LED0

-S1 BTN1, S0 a BTN0