Paso 1: Implementar el circuito en Verilog

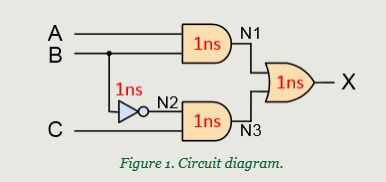

En este proyecto, vamos a implementar un circuito en Verilog y simular, habida cuenta de la demora. El circuito esquemático se muestra en la figura 1 anterior, y retardo de cada puerta está marcado en rojo.

El circuito tiene tres entradas (A, B, C) y una salida (X), por lo que la declaración del módulo va como sigue:

1 módulo () CombCirc

2 entrada,

3 entrada B,

4 entrada C,

salida 5 X

6);

7

8 / / Descripción del circuito

9

endmodule 10

Como tenemos que contar las herramientas sobre el retraso de cada una de las puertas, debemos definir el nombre de cada alambre interno.

1 alambre N1, N2, N3;

Ahora describimos cada puerta en el circuito uno por uno.

1 / / puerta y con retraso de 1ns

2 asignar #1 N1 = A y B;

3 / no cierre con retardo de 1ns

4 asignar #1 N2 = ~ B;

5 / retardo de puerta y con 1ns

6 asignar #1 N3 = N2 y C;

7 / retardo de puerta o con 1ns

8 asignar #1 X = N1 | N3;

Así el archivo Verilog que describe el circuito, con la información del retraso y escala de tiempo por cada retraso de cada puerta, mira como sigue:

1 ' calendario 1ns / 1ps

(módulo 2) CombCirc

3 entrada A,

4 entrada B,

5 entrada C,

salida de 6 X

7);

8

9 alambre N1, N2, N3;

10

11 / / puerta y con retraso de 1ns

12 asignar #1 N1 = A y B;

13 / no cierre con retardo de 1ns

14 asignar #1 N2 = ~ B;

15 / retardo de puerta y con 1ns

16 asignar #1 N3 = N2 y C;

17 / o puerta con 1ns retardo

18 asignar #1 X = N1 | N3;

19

endmodule 20